PCB设计中,一些特殊器件的布局要求,你想知道吗?

cathy -- 周五, 03/27/2020 - 17:50

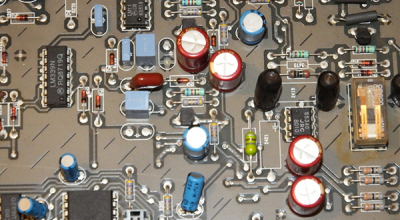

PCB器件布局不是一件随心所欲的事,它有一定的规则需要大家遵守。除了通用要求外,一些特殊的器件也会有不同的布局要求。

压接器件的布局要求

1)弯/公、弯/母压接器件面的周围3mm不得有高于3mm的元器件,周围1.5mm不得有任何焊接器件;在压接器件的反面距离压接器件的插针孔中心2.5mm范围内不得有任何元器件。

2)直/公、直/母压接器件周围1mm不得有任何元器件;对直/公、直/母压接器件其背面需安装护套时,距离护套边缘1mm范围内不得布置任何元器件,不安装护套时距离压接孔2.5mm范围内不得布置任何元器件。

3)欧式连接器配合使用的接地连接器的带电插拔座,长针前端6.5mm禁布,短针2.0mm禁布。

4)2mmFB电源单PIN插针的长针,对应单板插座前端8mm禁布。

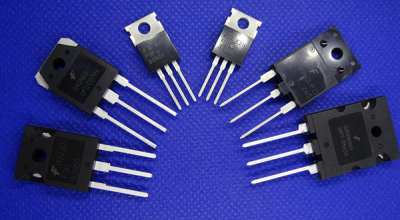

热敏器件的布局要求

1)器件布局时,热敏器件(如电解电容、晶振等)尽量远离高热器件。