技术博客 I 高速PCB Layout设计指南

cathy -- 周五, 02/21/2020 - 17:43

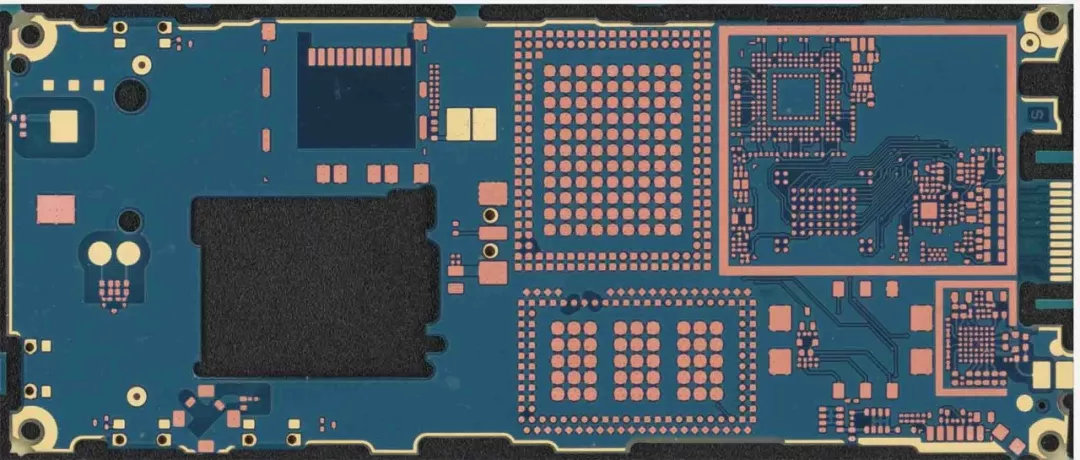

随着工业上对新型自动化、消费者对无线设备、医疗和航空航天等领域对技术发展的需求日益增长,这些领域对PCB的需求也在不断升级。如果我们能紧跟需求,设计出更小且更复杂的电路板,便能实现PCB设计工具市场的增长。对于PCB设计人员而言,这意味着在设计方面所面临的新挑战比以往任何时候都多。

高速PCB的layout设计基于我们作为PCB设计人员已经掌握的技能。元器件的布局仍需要符合可制造性设计以及测试要求,而走线规划仍将采用行业公认的宽度和间距设计规则。然而,本文提出了我们都需要熟悉的一些更严格的高速电路相关要求和设计实践。我们将对其中部分进行详细说明,帮助您快速理解高速layout设计。

从原理图开始