确定最佳印刷电路板布局的关键之一是了解信号返回电流的实际流动方式和方向,大多数设计人员只考虑信号电流的流向(显然是在信号迹线上),而忽略了返回电流所经过的路径。

为了解决上述问题,我们必须了解高频电流是如何在导体中流动的。

首先,最低阻抗的返回路径是在信号迹线正下方的平面上(不管这是电源还是地平面),因为这提供了最低的电感路径,这也产生了最小的电流环路面积可能。

其次,由于“集肤效应”,高频电流不能穿透导体,因此高频时导体中的所有电流都是表面电流。

这种影响将发生在所有频率超过30MHz的1盎司铜层,因此,PCB中的平面实际上是两个导体而不是一个导体。

在平面的上表面会有电流,在平面的下表面会有不同的电流或者根本没有电流。

当现有返回路径出现不连续时,就会出现严重的EMC问题。这些不连续性导致回流电流在更大的回路中流动,从而增加了电路板的辐射,增加了相邻线路之间的串扰,造成波形失真。

此外,在恒阻抗pcb板中,返回路径的不连续性会改变线路的特性阻抗。

下面讨论最常见的返回路径不连续。

地面/电源平面的开槽。当一根迹线通过相邻电源或接地线面上的槽时,为了绕过槽返回电流从迹线的下方转向,这使得它流经更大的环路。槽越长,环路面积越大。

关于地面上的开槽,我能说的最重要的一点就是不要它们!如果你有开槽,确保在相邻的层上没有迹线跨过它们。

如果你一定要跨过电源或地平面上的槽来传送信号,则在槽上放几个小的缝补电容,在线的两边各放一个(0.001或0.01 uF就足够了)。这将为返回电流跨过槽提供高频连续性,为了保证效果电容应该位于迹线0.1”的距离以内。

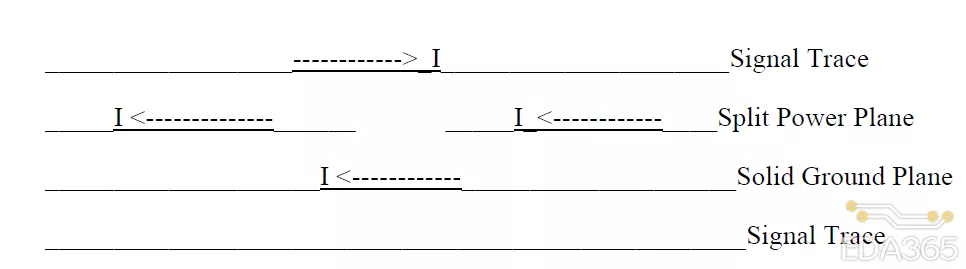

分割的地/电源平面。当迹线穿过相邻平面上的分割线时,如下面所示的4层板示例,返回的当前路径将被中断。

电流必须找到另一种方式跨过分割槽,这迫使它在一个更大的环路中流动。

在上面的示例中回流将通过最近的去耦电容走到实体的地平面,然后在分割槽的另一边回流必须找到另一个去耦电容以回到与迹线相邻的电源平面。

电源平面和地平面之间的平面间电容太小,除非在频率大大超过500MHz的情况下才有效,解决这一问题的最佳方案是避免关键信号跨分割。

在上面的例子中,信号应该在底层信号层上进行布线,因为底层信号层与实地平面相邻。

如果信号线必须跨平面分割,在分割平面上放置几个小的缝补电容,在迹线的两边各放一个。这将为跨分割提供高频连续性,同时保持两个分割平面之间的直流隔离。电容器应位于离迹线0.1”以内,并根据信号的频率取值0.001到0.01 uF。

然而,这远远不是一个理想的解决方案。因为返回电流现在必须通过一个via、一个trace、一个安装焊盘、一个电容、一个安装焊盘、一个trace,最后一个via到另一个分割面。这在返回路径增加了相当大的额外电感 (最小5至10 nH)。

如果在上面的例子中电源平面和地平面都分割了,你就真的有麻烦了,把电流如何通过分割平面边界的问题留给你们去解决。

在某些情况下,它可能会径直回到电源。如果你有一个分割的电源平面和分割的地平面唯一可接受的解决方案可能是确保没有信号迹线跨越分割的平面边界。

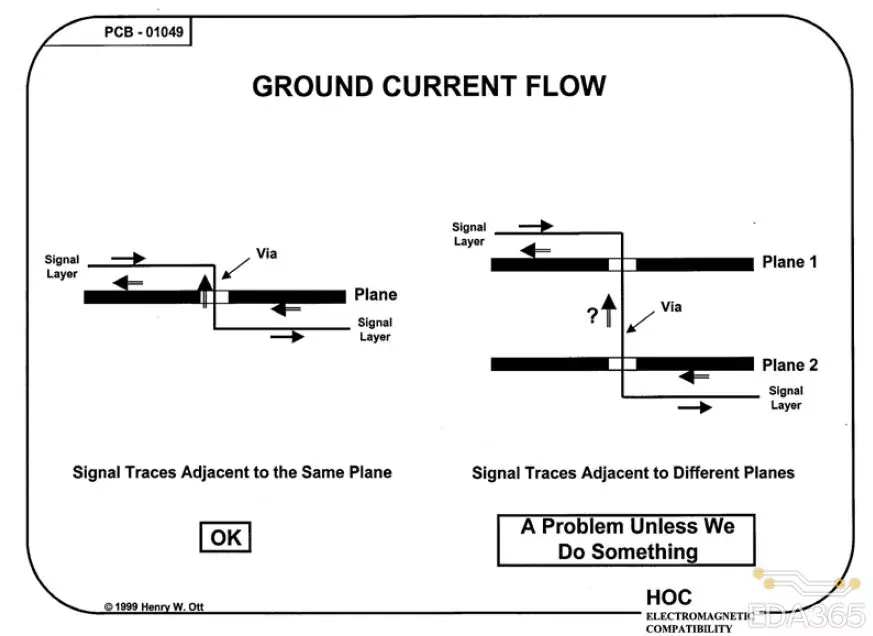

换参考平面。当一个信号迹线在PCB上从一个层换到另一个层时,由于返回电流也必须改变参考平面(见下面右图),所以返回电流路径被中断。

问题就变成了返回电流如何从一个平面到达另一个平面?

就像上面提到的分割平面一样,平面间电容通常不会大到足以产生作用,所以为了换参考面,回流电流必须流经最近的去耦电容。这显然增加了环路面积,由于前面所述的所有原因这是不可取的。

解决这个问题的一个办法是尽量避免关键信号(如时钟)换参考平面。如果你必须从一个电源平面切换到一个接地平面,你应该靠近信号过孔放置一个额外的去耦电容,以为信号回流在两个平面之间提供一个高频电流路径。

然而这依然不是一个理想的解决方案。因为现在的回流电流必须通过一个过孔、一段走线、一个安装焊盘、一个电容、一个安装焊盘,一段走线,最后一个过孔到另一个平面。这在返回路径增加了相当大的额外电感(通常5到10 nH)。

注意:如果两个参考平面是同一类型的(两个电源,或两个接地),您可以在紧邻信号过孔处放置一个过孔(接地到地或电源到电源),而不是一个电容。这是一个比使用电容更好的把两个平面连接在一起的解决方案,因为在返回路径增加的电感将大大减少。

参考同一平面的顶层和底层。当一个信号换层,并先参考同一平面的顶层然后参考底层时,我们仍然要问返回电流是如何从平面的顶层到底层的。由于“集肤效应”电流不能穿透平面,它只能在平面的表面流动。

为了打一个信号过孔穿过一个平面,必须在平面上提供一个间隙孔,否则信号将被短路到参考平面。间隙孔提供了一个连接平面顶层和底层的表面,并提供了一个回流电流从平面顶层流向平面底层的路径(见上面左图)。

因此,当一个信号通过一个过孔并继续在同一平面的另一侧走线时,返回电流不连续性不存在。因此,如果必须使用两个走线层,这是布关键信号的首选方法。

总结

高速时钟和其它关键信号应按下面规则布线(按优先顺序):

1、与平面相邻的层布线;

2、与同一平面相邻的两层布线;

3、在与同一类型的两个独立平面(接地或电源)相邻的两层上布线,并且在信号换参考面的地方用过孔将两个平面连接起来;

4、在与两个不同类型的独立平面(地面和电源)相邻的两层上布线,并且在信号换参考面的地方用电容将两个平面连接起来。

避免时钟或其它关键信号跨相邻平面的槽或分割。上述准则对所有承载高频信号的pcb都很重要,但对于具有恒定阻抗传输线的电路板来说则是非常重要的。

如果遵循本系列文章中关于层叠和避免返回电流不连续的指导原则, 将生产出更好的pcb,并避免与电路板相关的许多最常见的EMC问题。它不会向你保证是一个完美的PCB 布局,因为它离减少发射、提高抗扰度和改善电路板信号质量还有一段很长的路要走。

相关阅读:

PCB层叠EMC系列知识

应该收入囊中的PCB层叠EMC系列知识(二)

本文转载自: EDA365电子论坛(作者:余平放版主)

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理。