干货:详解高速电路设计阻抗匹配的几种方法

cathy -- 周二, 03/19/2019 - 15:07

为什么要阻抗匹配?

在高速数字电路系统中,电路数据传输线上阻抗如果不匹配会引起数据信号反射,造成过冲、下冲和振铃等信号畸变,当然信号沿传输线传播过程当中,如果传输线上各处具有一致的信号传播速度,并且单位长度上的电容也一样,那么信号在传播过程中总是看到完全一致的瞬间阻抗。由于在整个传输线上阻抗维持恒定不变,我们给出一个特定的名称,来表示特定的传输线的这种特征或者是特性,称之为该传输线的特征阻抗。

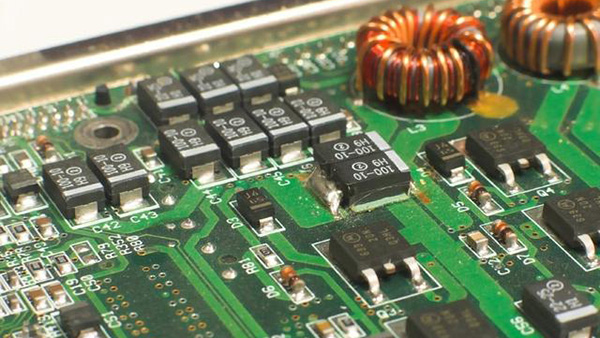

特征阻抗是指信号沿传输线传播时,信号感受的瞬间阻抗的值。特征阻抗主要参数与PCB导线所在的板层、PCB所用的材质(介电常数)、走线宽度、导线与平面的距离等因素有关,与走线长度无关。特征阻抗可以使用软件计算。高速PCB布线中,一般把数字信号的走线阻抗设计为50欧姆,这是个大约的数字。一般规定同轴电缆基带50欧姆,频带75欧姆,对绞线(差分)为100欧姆。

而减小反射的方法是根据传输线的特性阻抗在其发送端串联端接使源阻抗与传输线阻抗匹配或者在接收端并联端接使负载阻抗与传输线阻抗匹配,从而使源反射系数或者负载反射系数为零。常用的端接方式为:串联端接、简单的并联端接、戴维宁端接、RC网络端接等。

下面我们将分别对这几种端接方式进行分析

1、串联端接