无论是早期的收音机、电视机到计算机、移动通讯终端,还是目前的移动智能终端的4G/5G技术研究、人工智能、云计算、AR/VR等技术,这些技术发展无疑都对MCU、基带、FPGA等组成的这些高速电路的计算量要求越来越大,也越来越快。这些都推动着高速电路的蓬勃发展。随着电路数据速度的暴增,高速电路的学习、应用、研究也越来越难,门槛也越来越高。作为高速电路应用设计发展的工程师们必然要学习很多,同样也会遇到不少问题。

正如很多硬件工程师在看高速电路时,都会经常看到串一些小电阻,如22欧姆,但是也不是一定串。同样场合有的串,有的不串。这是为什么呢?

这个电阻有两个作用

第一是阻抗匹配。因为信号源的阻抗很低,跟信号线之间阻抗不匹配,串上一个电阻后,可改善匹配情况,以减少反射,避免振荡等。

严格来讲,当高速电路中,信号在传输介质上的传输时间大于信号上升沿或者下降沿的1/4时,该传输介质就需要阻抗匹配。一般当PCB走线的长度大于其传输信号的波长的1/10时,我们就需要考虑阻抗匹配。(在高频高速电路时,信号线应用传输线理论去解释,一般低频低速电路,不在适用)。

比如,100MHz以上的高速数字电路就可以考虑阻抗匹配了主要是基于阻抗匹配方面的考虑,以达到时序统一,延迟时间,走线电容等不会超过范围!原因在于LAYOUT时可能走线方面不是很匹配!

另外,高速信号线串的小电阻,LAYOUT时应该把它放在CPU端还是放在信号的终端好些呢 ?

一般的做法是在信号源端串小电阻,在信号终端并一个小电阻。在信号源端串一个小电阻,没有公式的理论:一般传输线的特征阻抗为50欧姆左右,而TTL电路输出电阻大概为13欧姆左右,在源端串一个33欧姆的电子,13+33=46大致和50相当,这样就可以抑制从终端反射回来的信号再次反射。在信号接收终端并一个小电阻,没有公式的理论:若信号接收端的输入阻抗很大,所以并接一个51欧姆的电阻,电阻另一端接参考地,以抑制信号终端反射。信号接收终端串接电阻,从抑制信号反射的角度考虑,只有终端输入的电阻小于50欧姆。但IC设计时,考虑到接收能量,不会将接收端的收入电阻设计得小.。

常用传输线阻抗如下:

1.CVBS视频信号线 75欧姆

2.MIPI、LVDS信号线 100欧姆

3.USB信号线 90欧姆

4.2G/3G/4G/WIFI天线 50欧姆

5.DDR 50欧姆

第二是可以减少信号边沿的陡峭程度,从而减少高频噪声以及过冲等。

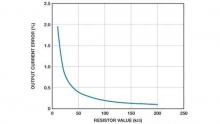

因为串联的电阻,跟信号线的分布电容以及负载的输入电容等形成一个RC电路,这样就会降低信号边沿的陡峭程度。大家知道,如果一个信号的边沿非常陡峭,含有大量的高频成分,将会辐射干扰,另外,也容易产生过冲。

而高速在数据电平变化时,电压和电流都会迅速变化,造成较大瞬态变化(di/dt、dv/dt),这其中便含有大量的高频成分,抑制干扰源就是尽可能的减小干扰源的du/dt,di/dt。这是抗干扰设计中最优先考虑和最重要的原则,常常会起到事半功倍的效果。减小干扰源的du/dt主要是通过在干扰源两端并联电容来实现。减小干扰源的di/dt则是在干扰源回路串联电感或电阻来实现。

本文转载自:今日头条-何雪涛硬件设计

声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有,如涉及侵权,请联系小编邮箱:cathy@eetrend.com 进行处理。