如何避免和消除自激振荡?(下)

cathy -- 周四, 07/23/2020 - 11:14

自激振荡像得病一样,重在防御。可从以下方面入手。

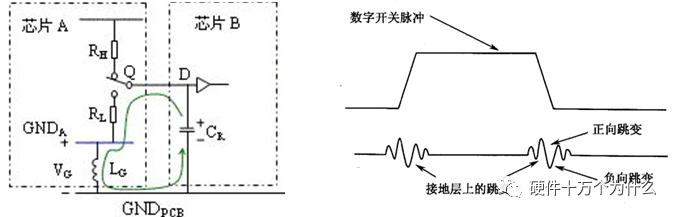

1)设计 PCB 时,尽量减小杂散电容,特别是CIN-。下图进行说明:

同一层的两个相邻节点间。比如某根信号线,和周边的覆铜 GND 之间,以及和周边的焊点之间有杂散电容C1;

不同层上下之间。比如元件层的线,和焊接层的大面积 GND 之间,如图中 C2;

一般的,杂散电容可以达到 pF 数量级。这是不可忽视的。这些杂散电容和电路中的电阻,很容易形成低通网络,有可能引起电路稳定性下降。

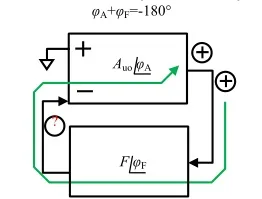

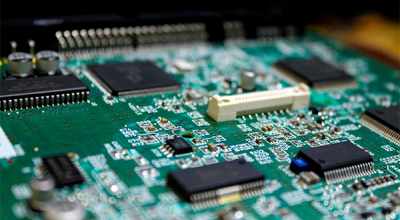

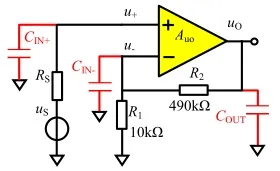

电路举例,如下图:

设计一个同相比例器,做成实际电路板后,就出现了三个杂散电容:CIN+、CIN-、COUT