【技术干货】电路入门:关于二极管、晶体管、FET你了解多少呢?

cathy -- 周三, 12/19/2018 - 09:36

上次我们学习了无源元件,今天我们接着来复习一下半导体以及使用了半导体的有源元件-二极管、晶体管、FET。

相关阅读:

【技术干货】电路入门:关于无源元件你了解多少呢?

导电能力介于导体与绝缘体之间的物质 - 半导体

硅和锗是位于银、铝等导体和石英、陶瓷等绝缘体之间,用于制造半导体器件的原材料,具有一定电阻率。不同的物质其产生的不同电阻率是由于可移动的电子量不同引起的。这种可移动电子叫“自由电子”。一般我们把可以通过向其摻入杂质来改变自由电子的数量,并可控制电流动的物质称为半导体。

根据电流流动的构造,可将半导体分为N型和P型两类。

半导体的电流流通原理

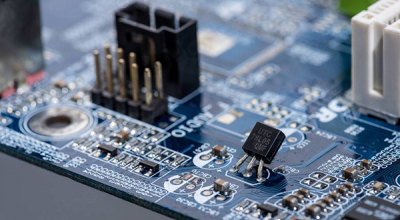

(1) N型半导体