偏置电流源电路的对与错

cathy -- 周五, 01/22/2021 - 14:22

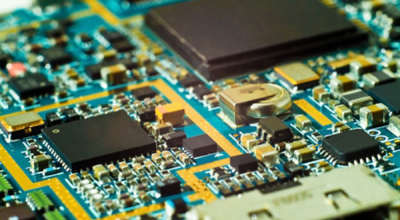

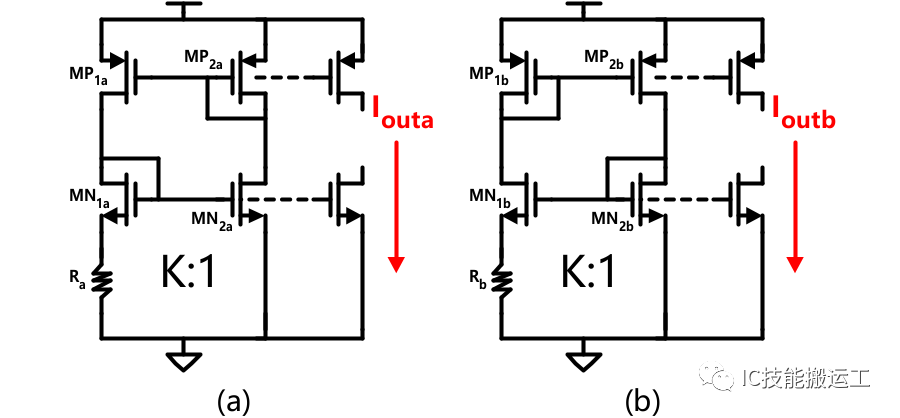

下面的电流源偏置电路究竟哪个结构是对的?几乎每个模拟IC课程都会讲这个例子,可是始终有人搞不清楚。

常见的电流源偏置电路

在介绍gm/Id的集成电路设计方法时,有一个实例就是设计一个简单的电流源偏置,关于电流源偏置的原理也在其中仔细推导。

上图中的两个电路结构是应聘模拟集成电路设计岗位时最常见的电路结构之一,经常有面试官拿这个结构出一些问题。

问题很简单:假设所有MOS管都工作在饱和区,NMOS尺寸比例如图中标注所示(K>1),那么上图中哪个电路工作的更好,给出合理的理由?

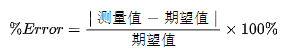

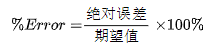

有两个关于该电路的推导,分别是输出电流表达式与两个NMOS跨导的比值,这两个结论会在后面用到。