作者:吴均 一博科技高速先生团队队长

第一个争议性话题来了:等长越严格,时序裕量越大,系统越稳定!

这句话应该有很多硬件工程师是同意的,所以我们也经常能看到类似的规则:

-

DDR3同组的DQ和DQS需要+/-1mil等长

-

DDR3同组的CLK和Add/Ctrl/Cmd需要+/-10mil等长

-

DDR3的CLK和DQS需要+/-100mil等长

-

PCIE3.0,差分对内需要+/- 0mil等长,没有误差

……

类似的规则还可以衍生为:

-

线间距越大约好,减少串扰

-

走线需要两面严格参考完整地平面

……

类似的规则,用现在最流行的话来说,应该就是“理都懂”,但是臣妾做不到呀!

这里忍不住要吐槽一下:随着PCB设计这个工种慢慢从硬件设计中独立出来,大部分公司里面PCB设计工程师和硬件原理工程师不是同一个人。所以有些EE会想当然或者很理直气壮把很严格的规则提交给上下游,反正需要绕线的不是我……更不用说外包的PCB设计了,更是占住了甲方的位置,你们给我往死里绕线。

当然,更多的硬件原理工程师并不是这么想的,只是当这个项目落在自己头上的时候,战战兢兢,如履薄冰,想把一切事情做到完美。

等长与等时

之前的文章有提过,所有的等长都不是目的,设计的目的是等时。所以我们首先要知道,+/-10mil对应的时间是多少?貌似+/-1mil等长比+/-10mil严格了10倍,我的时序裕量会不会好很多?

大家应该还记得高速先生王锐写的那篇文章:《信号是怎样传输的?》,没看过的可以翻出来再看看。文章的最后,给出了一个案例:同一种阻值的走线,微带线时延是145.9ps/in,带状线时延为173.6ps/in。

我们需要记住的值是每英寸145~170ps,对于带状线来说,每ps延时对应的走线长度是6mil左右。所以,+/-10mil等长和+/-1mil等长,在时间上的差异不超过3ps。再回头看看我们的系统,有多少是真正需要3ps裕量的?

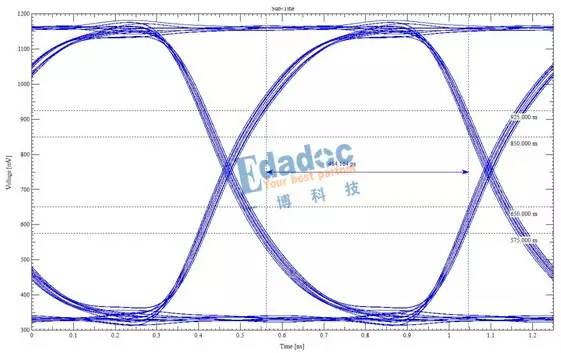

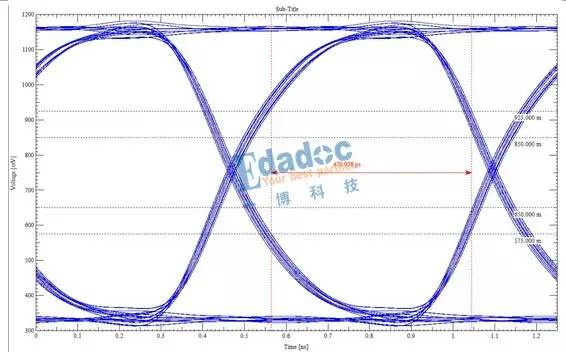

上图是同一个波形,不同的两个人测量的时序窗口大小,有4个多ps的误差。测量的波形也是一样,大家都有这样的经验。

高速先生有时候为了说服一些客户不要纠结在等长是1mil还是5mil,或者劝告说完全等长是没有意义的,我们也是拼了,下面是我们用过的一些比喻:

-

蚊子再小也是肉,你要吃蚊子我忍了,但是蚊子腿就不要去吃了吧

-

中华民族艰苦节约的良好美德,但是现在的社会,就不用纠结于要不要省1毛钱了吧

-

……

如果你能理解以上比喻,那么应该可以理解:

大部分的系统,不管是DDR3的数据分组还是PCIE3或者10G Base KR的差分对内,等长做到5mil已经足够了。速率更低的系统,还可以放宽更多。

这篇文章的篇幅已经比较长,所以主要讨论等长不需要过度考虑这一个问题点。另外一个相关的话题是:严格等长会不会带来负面影响,会不会成为系统失效的根源。

相关阅读:

PCB设计十大误区-绕不完的等长(一)

PCB设计十大误区-绕不完的等长(二)

PCB设计十大误区-绕不完的等长(三)

本文转载自:高速先生(作者:吴均)

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理(联系邮箱:cathy@eetrend.com)。