关于低通滤波器、高通滤波器,积分电路、微分电路的那些事儿~

cathy -- 周二, 07/24/2018 - 15:19

输出信号与输入信号的积分成正比的电路:积分电路

输出信号与输入信号的微分成正比的电路:微分电路

1)一阶RC低通滤波器

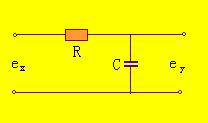

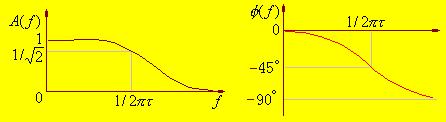

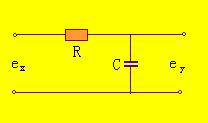

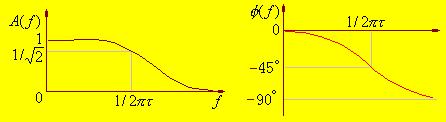

RC低通滤波器的电路及其幅频、相频特性如下图所示。

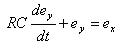

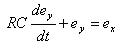

设滤波器的输入电压为ex输出电压为ey,电路的微分方程为:

这是一个典型的一阶系统。令=RC,称为时间常数,对上式取拉氏变换,有:

输出信号与输入信号的积分成正比的电路:积分电路

输出信号与输入信号的微分成正比的电路:微分电路

1)一阶RC低通滤波器

RC低通滤波器的电路及其幅频、相频特性如下图所示。

设滤波器的输入电压为ex输出电压为ey,电路的微分方程为:

这是一个典型的一阶系统。令=RC,称为时间常数,对上式取拉氏变换,有:

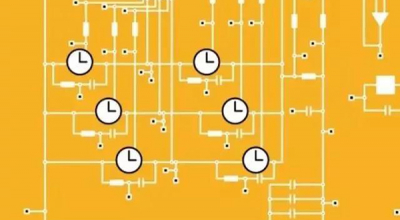

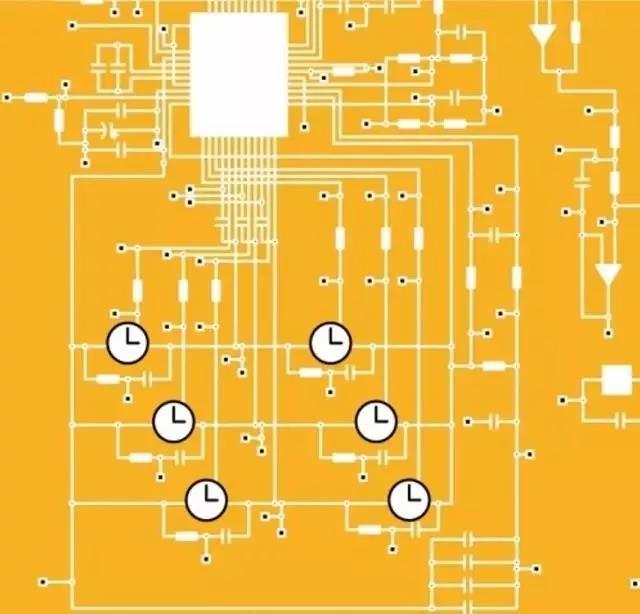

1、AHB系统总线分为APB1(36MHz)和APB2(72MHz),其中2>1,意思是APB2接高速设备

2、Stm32f10x.h相当于reg52.h(里面有基本的位操作定义),另一个为stm32f10x_conf.h专门控制外围器件的配置,也就是开关头文件的作用

3、 HSE Osc(High Speed External Oscillator)高速外部晶振,一般为8MHz,HSI RC(High Speed InternalRC)高速内部RC,8MHz

4、 LSE Osc(Low Speed External Oscillator)低速外部晶振,一般为32.768KHz,LSI RC(Low Speed InternalRC)低速内部晶振,大概为40KHz左右,提供看门狗时钟和自动唤醒单元时钟源

5、 SYSCLK时钟源有三个来源:HSI RC、HSE OSC、PLL

作者:邹林

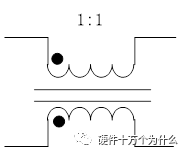

1、共模电感原理

在介绍共模电感之前先介绍扼流圈,扼流圈是一种用来减弱电路里面高频电流的低阻抗线圈。为了提高其电感扼流圈通常有一软磁材料制的核心。共模扼流圈有多个同样的线圈,电流在这些线圈里反向流,因此在扼流圈的芯里磁场抵消。共模扼流圈常被用来压抑干扰辐射,因为这样的干扰电流在不同的线圈里反向,提高系统的EMC。对于这样的电流共模扼流圈的电感非常高。共模电感的电路图如图1所示。

共模信号和差模信号只是一个相对量,共模信号又称共模噪声或者称对地噪声,指两根线分别对地的噪声,对于开关电源的输入滤波器而言,是零线和火线分别对大地的电信号。虽然零线和火线都没有直接和大地相连,但是零线和火线可以分别通过电路板上的寄生电容或者杂散电容又或者寄生电感等来和大地相连。差模信号是指两根线直接的信号差值也可以称之为电视差。

假设有两个信号V1、V2

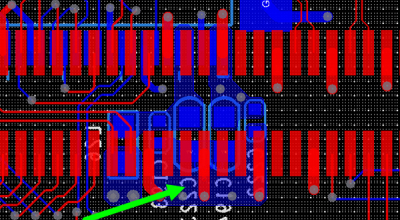

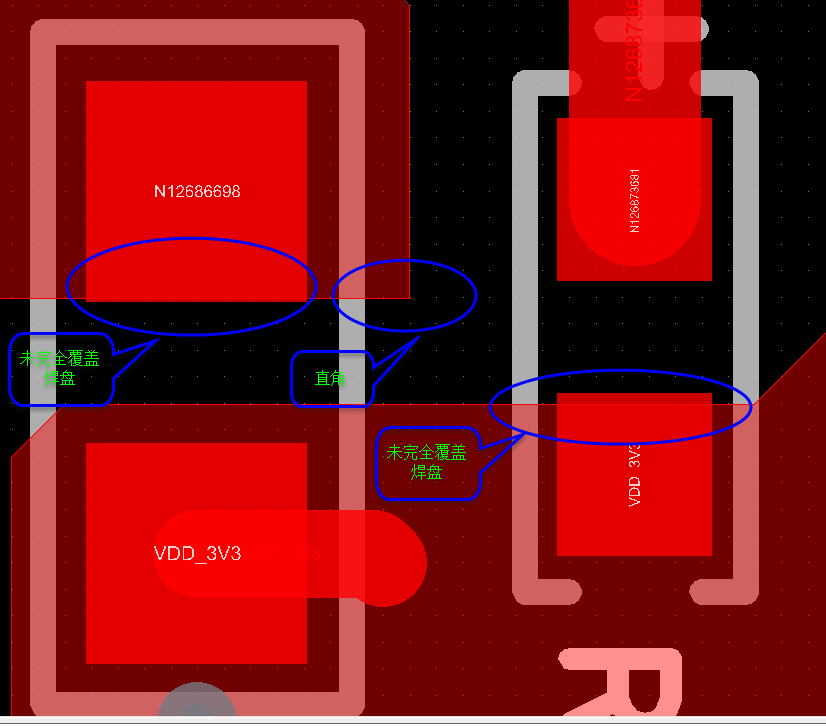

1.覆铜覆盖焊盘时,要完全覆盖,shape 和焊盘不能形成锐角的夹角。

2.尽量用覆铜替代粗线。当使用粗线时,过孔通常最好为非通常走线过孔,增大过孔的孔径和焊盘。

修改后:

3.尽量用覆铜替换覆铜+走线的模式,后者常常产生一些小尖角和直角使用覆铜替换走线:

在英语中,我们经常使用“comparing apples to apples”来表示我们在类似事物之间进行公平比较。另一方面,如果用“comparing apples to oranges”,那么我们的意思相反。

有时,尽管我们尽了最大的努力,但我们的实验室测量结果可能会产生“apples to bruised apples”的影响。在本月的帖子中,我将在“TheCase of the Discrepant Scope Measurements”中提供一个相对常见的例子。

最初的案例

几年前,我正在支持振荡器客户,我们遇到了相关问题,即他的测量与我的相比。与规格和部件的典型性能相比,他的周期抖动测量值没有任何意义。

我知道我们要用类似的板,电缆,终端,测试设备,并至少尝试相同的测量。我们甚至有非常相似的示波器。当我让他向我发送波形图时,我开始怀疑他的设备是否有些不对劲。答对了!他的波形是我的波形的一小部分,我知道这很可能是差异的根源。

在这篇文章中,我将回顾一个经验法则,该法则可用于估算RMS周期间抖动,前提是你知道RMS周期抖动。我首先在实验室中观察了这个经验法则,并随后了解了更多。

该经验法则是什么?

该法则很简单。如果周期抖动分布是高斯或正态分布,则周期间抖动可以根据周期抖动估算如下:

Jcc (RMS)= sqrt(3) * Jper (RMS)

PCB布局设计中格点的设置技巧

设计在不同阶段需要进行不同的各点设置,在布局阶段可以采用大格点进行器件布局;

对于IC、非定位接插件等大器件,可以选用50~100mil的格点精度进行布局,而对于电阻电容和电感等无源小器件,可采用25mil的格点进行布局。大格点的精度有利于器件的对齐和布局的美观。

PCB布局规则:

1、在通常情况下,所有的元件均应布置在电路板的同一面上,只有顶层元件过密时,才能将一些高度有限并且发热量小的器件,如贴片电阻、贴片电容、贴片IC等放在低层。

2、在保证电气性能的前提下,元件应放置在栅格上且相互平行或垂直排列,以求整齐、美观,在一般情况下不允许元件重叠;元件排列要紧凑,元件在整个版面上应分布均匀、疏密一致。

3、电路板上不同组件相临焊盘图形之间的最小间距应在1MM以上。

4、离电路板边缘一般不小于2MM.电路板的最佳形状为矩形,长宽比为3:2或4:3.电路板面尺大于200MM乘150MM时,应考虑电路板所能承受的机械强度。

PCB布局技巧:

在PCB设计中,可以通过分层、恰当的布局布线和安装实现PCB的抗ESD设计。在设计过程中,通过预测可以将绝大多数设计修改仅限于增减元器件。通过调整PCB布局布线,能够很好地防范ESD。

来自人体、环境甚至电子设备内部的静电对于精密的半导体芯片会造成各种损伤,例如穿透元器件内部薄的绝缘层;损毁MOSFET和CMOS元器件的栅极;CMOS器件中的触发器锁死;短路反偏的PN结;短路正向偏置的PN结;熔化有源器件内部的焊接线或铝线。为了消除静电释放(ESD)对电子设备的干扰和破坏,需要采取多种技术手段进行防范。

在PCB板的设计当中,可以通过分层、恰当的布局布线和安装实现PCB的抗ESD设计。在设计过程中,通过预测可以将绝大多数设计修改仅限于增减元器件。通过调整PCB布局布线,能够很好地防范ESD。以下是一些常见的防范措施。

尽可能使用多层PCB,相对于双面PCB而言,地平面和电源平面,以及排列紧密的信号线-地线间距能够减小共模阻抗和感性耦合,使之达到双面PCB的1/10到1/100。尽量地将每一个信号层都紧靠一个电源层或地线层。对于顶层和底层表面都有元器件、具有很短连接线以及许多填充地的高密度PCB,可以考虑使用内层线。

最常见的是以下两种

① 超过变量128后必须使用compact模式编译,实际的情况是只要内存占用量不超过 256.0 就可以用 small 模式编译

② 128以上的某些地址为特殊寄存器使用,不能给程序用.与 PC 机不同,51 单片机不使用线性编址,特殊寄存器与 RAM 使用重复的重复的地址。但访问时采用不同的指令,所以并不会占用 RAM 空间。

③是否把一些固定的代码存贮到了CODE区。如果把没变化的数据也存储到DATA去,就太浪费了!

由于内存比较小,一般要进行内存优化,尽量提高内存的使用效率。

以 Keil C 编译器为例,small 模式下未指存储类型的变量默认为data型,即直接寻址,只能访问低 128 个字节,但这 128 个字节也不是全为我们的程序所用,寄存器 R0-R7必须映射到低RAM,要占去 8 个字节,如果使用寄存组切换,占用的更多。

所以可以使用 data 区最大为 120 字节,超出 120 个字节则必须用 idata 显式的指定为间接寻址,另外堆栈至少要占用一个字节,所以极限情况下可以定义的变量可占 247 个字节。当然,实际应用中堆栈为一个字节肯定是不够用的,但如果嵌套调用层数不深,有十几个字节也够有了。

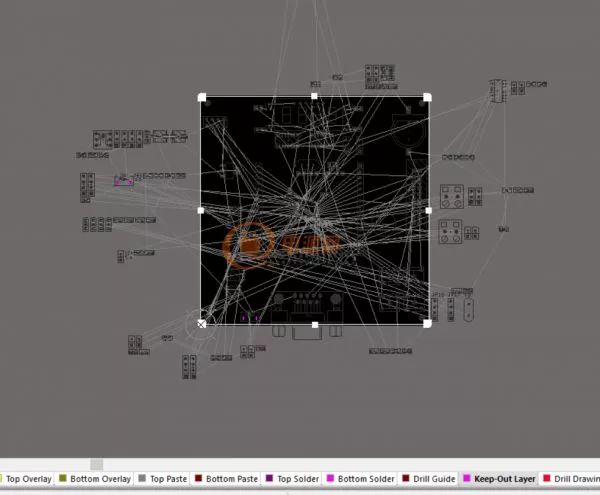

布线篇在前面基本都讲完了,接下来我们讲讲后期处理篇~ 到了后期篇,再进行一些工作,整个PCB的工作就结束了,想想还是很兴奋的~

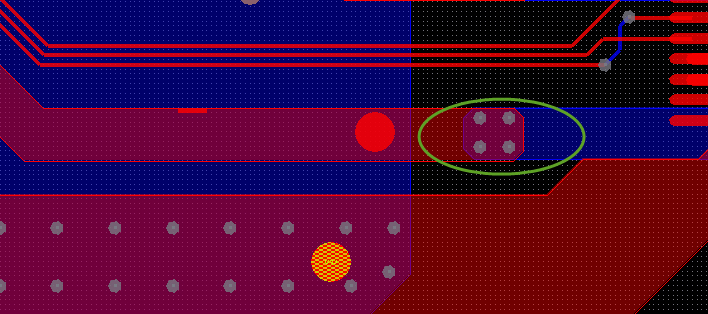

首先检查GND网络,是否都有加回流孔接地,具体操作按住CTRL 单击地网络,然后按{进行网络高亮,看一下有没有哪里没加,加一下。

【铺铜篇】加完以后就要开始铺铜(顶层和底层都要铺的)了,对于最后一个网络进行连接,第一步在Keepout层选中板框,如下:

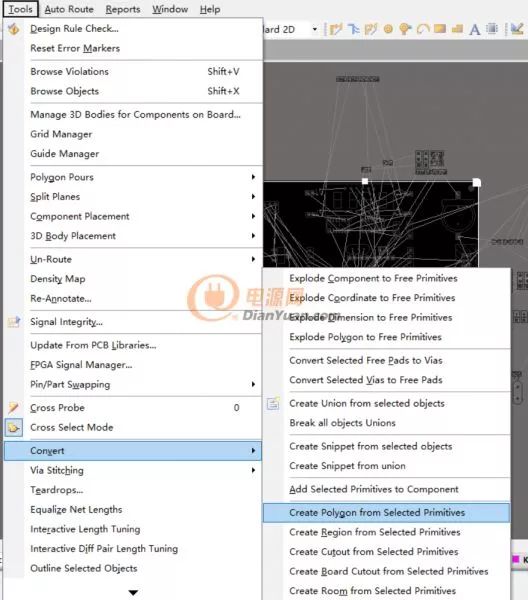

【铺铜篇1】执行tools里面的convert里面创建铜皮,没有太多要讲的,操作就要按部就班,具体如下:

【铺铜篇2】:铺铜完毕后,会发现有很多的尖甲铜皮,不处理会产生天线效应,如下: