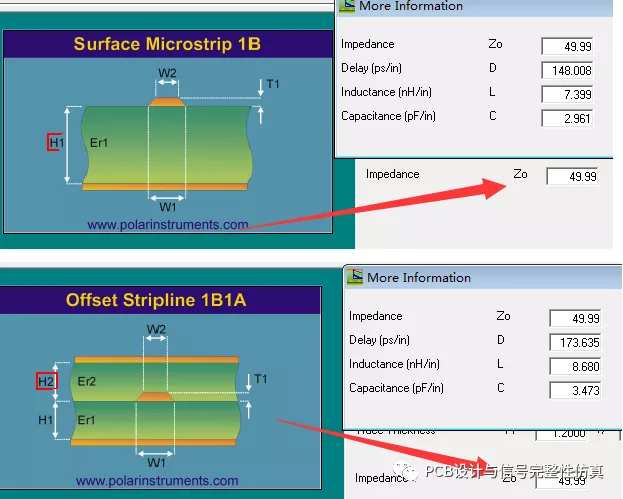

在上篇文章介绍信号在不同层传播速度时,我们设定了一个限制条件。那就是在阻抗50Ω的情况下计算传播速度:

难道阻抗还会对信号速度产生影响?

没错,阻抗确实会对速度造成影响。

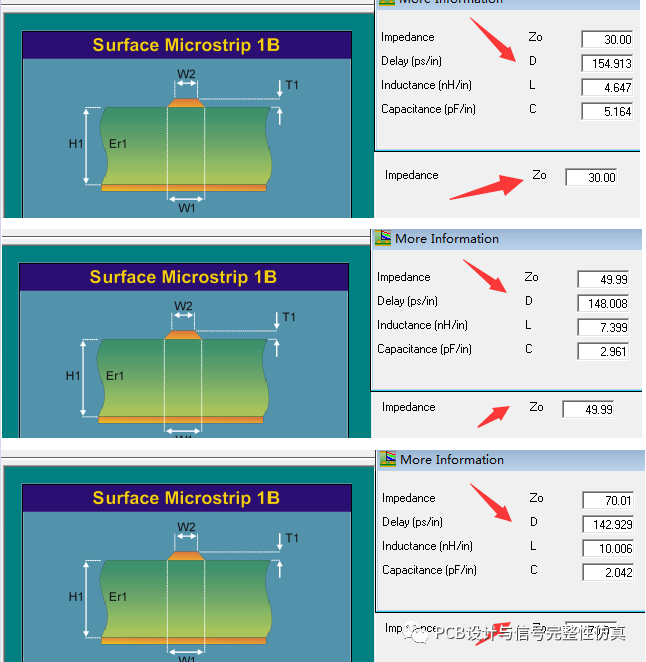

得出这个结论很简单,使用SI9000就可以验证。当阻抗控制分别为30、50、70的时候分别求解传输速度:

可以看见阻抗越高,信号传播速度也就越快。对于此次我们计算的这个模型而言,阻抗70Ω时约为7mil/ps,阻抗30Ω时为6.5mil/ps。也就是在这种情况下如果存在1000mil长度的走线阻抗不相同,就会带来约12ps折合近70mil的长度差异。依然是一个不小的差异。

在设计中比较常见的阻抗偏差主要存在于一些BGA器件走线需要以较细的线宽走出一段距离后才能恢复正常阻抗,那么在这段区域会存在阻抗偏高。

以及在多负载DDR中比较常见的容性负载补偿,通常会降低主干道的阻抗,增加容性负载区域的阻抗。这些做法由于不能严格统一各个阻抗线的走线长度,因此一定程度上都会带来延时上的一些差异。

到目前为止我们已经从绕线方式、传播速度、阻抗这三个方面来介绍了一些虽然看上去长度上等长了,但实际上并未等延时的情况。实际设计中会造成延时误差的因素也远不止这三个,篇幅的关系就不再展开。

在这些内容中,计算出来的值动辄就是几十几百个MIL的长度差异,有些同学可能被吓住了。会产生疑问:“照这个情况看,感觉自己如果按照延时来绕线,永远也拉不完等长了”

也有一些同学觉得没有什么意义:“这些我平常都没去注意,可我的系统还不是运行得好好的,有什么意思呢?”

关于这两个疑惑,会在下期内容中给大家解释,同时下期也将是我们关于科学绕等长的最后一期。

相关阅读:

如何科学绕等长(一)

如何科学绕等长(二)

本文转载自: PCB设计与信号完整性仿真(作者:十四岁的十四 )

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理。