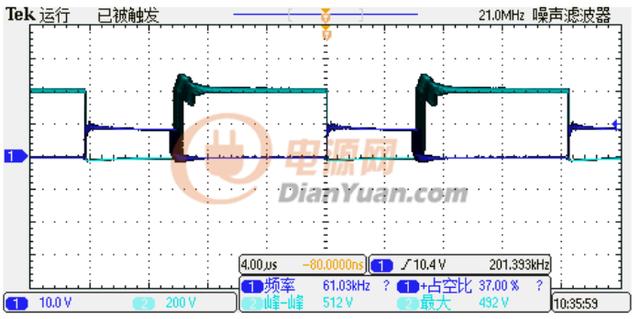

电源噪声滤波器的基本原理与应用方法

cathy -- 周四, 05/21/2020 - 16:05

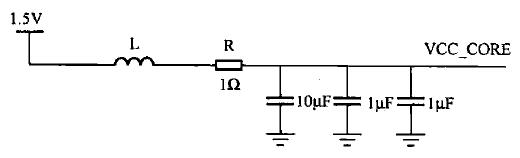

随着现代科学技术的飞速发展,电子、电力电子、电气设备应用越来越广泛,它们在运行中产生的高密度、宽频谱的电磁信号充满整个空间,形成复杂的电磁环境。复杂的电磁环境要求电子设备及电源具有更高的电磁兼容性。于是抑制电磁干扰的技术也越来越受到重视。接地、屏蔽和滤波是抑制电磁干扰的三大措施,下面主要介绍在电源中使用的EMI滤波器及其基本原理和正确应用方法。

电源设备中噪声滤波器的作用

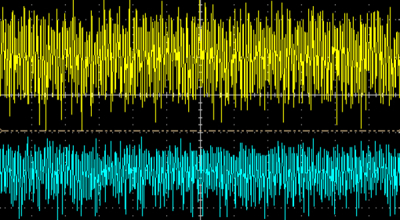

电子设备的供电电源,如220V/50Hz交流电网或115V/400Hz交流发电机,都存在各式各样的EMI噪声,其中人为的EMI干扰源,如各种雷达、导航、通信等设备的无线电发射信号,会在电源线上和电子设备的连接电缆上感应出电磁干扰信号,电动旋转机械和点火系统,会在感性负载电路内产生瞬态过程和辐射噪声干扰;还有自然干扰源,比如雷电放电现象和宇宙中天电干扰噪声,前者的持续时间短但能量很大,后者的频率范围很宽。另外电子电路元器件本身工作时也会产生热噪声等。

这些电磁干扰噪声,通过辐射和传导耦合的方式,会影响在此环境中运行的各种电子设备的正常工作。