为什么要在意电源系统的信号完整性?

随着人工智能、物联网、VR/AR等技术的发展,相应的硬件技术也在日新月异。芯片的集成度也越来越高,内部的晶体管数量也越来越多。但是芯片的外片管脚是有限的,只能依靠内外部有限的供电管脚为内部数以亿计的晶体管供电。对于内部各个晶体管的操作通常由内核时钟及片内外设时钟来同步的,由于内部延时的原因,更晶体管的转换状态是不可能一致的。这就会导致电源噪声在系统内部相互传递。

除了影响芯片内部的正常工作状态,他还会对晶振、PLL、DLL的抖动特性及AD/DA转换电路的精度产生影响。

电源系统的噪声余量分析

绝大多数芯片都会给出一个工作电压的范围,这个值通常是5%。而这些限制主要考虑两个部分,一个是电源芯片稳压的误差,而另外一个则是电源噪声的峰值幅度。

在我们选择的电源芯片即使可以达到要求,也要看芯片达到要求的条件,如:外围器件的电阻电容的参数影响、工作环境是否符合稳压芯片的的推荐环境、负载状况是否满足条件等。

电源噪声是如何产生的呢?

电源噪声主要来源与三个方面。

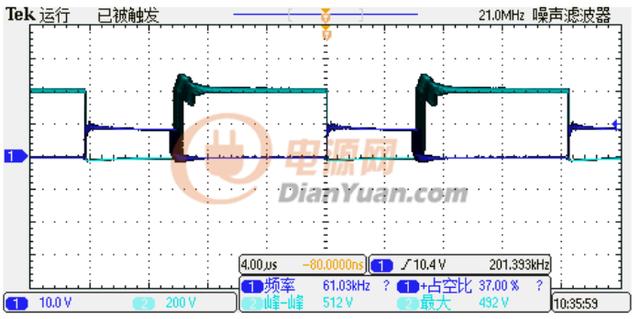

1、稳压芯片本身的输出并不是恒定的,会有一定的纹波。

2、稳压电源无法实时及时响应负载的对于电流需求的变化。

稳压电源芯片通常通过感值电压变化来调整其输出电流,从而把电压调整回额定的输出电压。多数常用的稳压电源的负载响应的时间通常在毫秒级甚至是微妙级。因此对于负载变化频率在几百千赫兹的以内时,稳压源都为做出较好的反应,保证电压输出不会出现跌落。但是当负载变化的超出这一频率时,往往会导致输出电压的跌落,从而产生电源噪声。

3、负载变化电流在电源路径阻抗及地路径阻抗产生的电压压降。

硬件物联网人工智能设计

本文转载自:何雪涛硬件设计

转载地址:https://www.toutiao.com/i6519258670054769160/

声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有,如涉及侵权,请联系小编邮箱:cathy@eetrend.com 进行处理。