当我写这篇文章正值感恩节。从技术角度来说,我感谢的前几代工程师为我们这个行业奠定了基础,为当代的工程师提供了培训,指导或其他方面的机会。这让我想起了一个特别的话题――拆分终端(The Split Termination)。

拆分终端

这个月,我想就Timing Knowledge Base板块的“Terminating Differential Transmission Lines toMinimize CM Noise”一文中首先介绍的一个话题展开一些讨论。那篇文章描述了一个相对简单但非常实用的差分电路终端,这个终端在很多年前由一位经验丰富的EMI工程师向我提出。

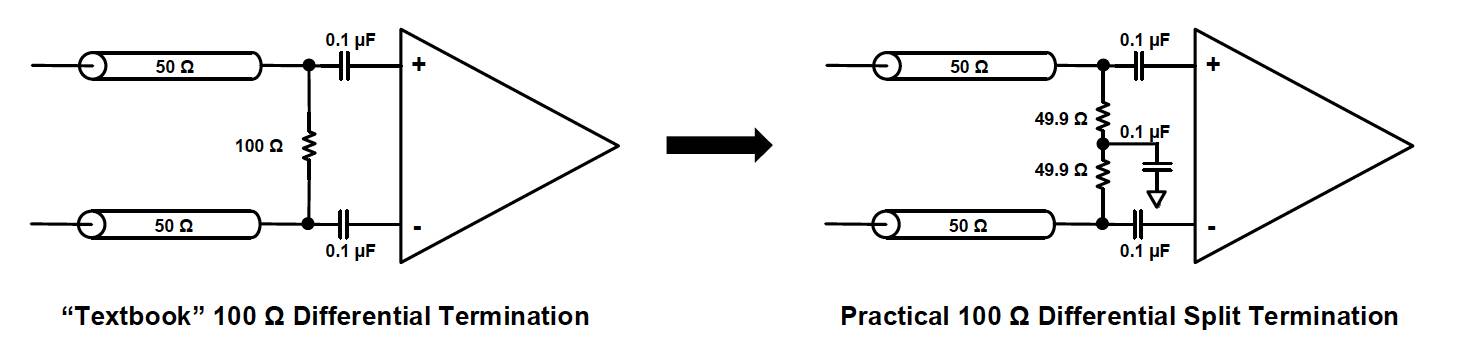

我在学校里从来没有碰到过这样的东西,但是我已经无处不在地使用它了。这是就是本月的主题,拆分终端的情况。下面的图表达了这个想法。我们一般从左手的“教科书”终端移到右手更实际的终端。

许多输出时钟格式(如CML,LVDS和LVPECL)都是差分布线和端接的。这通常被表示为一对单端标称非耦合50Ω传输线(每个极性一个),在电路的远端或接收器端端接一个理想的100Ω电阻。这就是左侧描述的“教科书”式100Ω差分端接。

但是,考虑在使用与噪声相同的电压信号同时驱动两条输入传输线时会发生什么情况。与通常的差模(DM)情况相反,这是共模(CM)情况。由于100端接电阻两端的电压相同,因此没有电流流过。因此,CM信号根本“看不见”端接电阻,高阻抗接收器看起来像是开路的。(在这个例子中,CM传输线阻抗是50Ω// 50Ω= 25Ω)。所以从CM的角度来看,我们有一个“噪声”信号发生器将25Ω传输线路驱动到一个开路,这意味着CM噪声,可能很多次。

CM噪声可能源于电源和串扰影响两条传输线的情况。此外,即使你的电路板没有那么多噪声,CM噪声也可能来自不平衡的传输线或歪斜,这是非常普遍的。

我们怎么能终止DM和CM?右侧的实际拆分终端是T网络尝试这样做的要求,只需要两个以上的元件和交流耦合接地。请注意,这种特殊的终端不会增加驱动器上的直流负载。

还有其他方法,但是这些可能需要更多的元件,更多的DC电流消耗,更多的匹配或可能的偏置电压。(顺便说一下,这种差分分离端接不应与LVPECL上拉和下拉端接混淆,后者有时也被称为“分离”端接)。

分离终端明确地分解负载终端,并在中心处实施一个实际的AC GND。现在,CM电流将流动,CM信号将在感兴趣的频率上“看到”匹配的阻抗。 49.9Ω选择是与标称50Ω最接近的1%。相反,差分驱动的信号不会将中心抽头电容“看到”GND。

应用细节

直觉正确地表明,中心抽头电容器强制CM电压看到GND的低阻抗。 0.1μF的值是一个很好的值,可以根据需要进行调整。有几个定量的方法来确定电容器的大小。

(1)调整电容的大小,使电容在最大预期的Δt歪斜(reference)期间保持稳定。

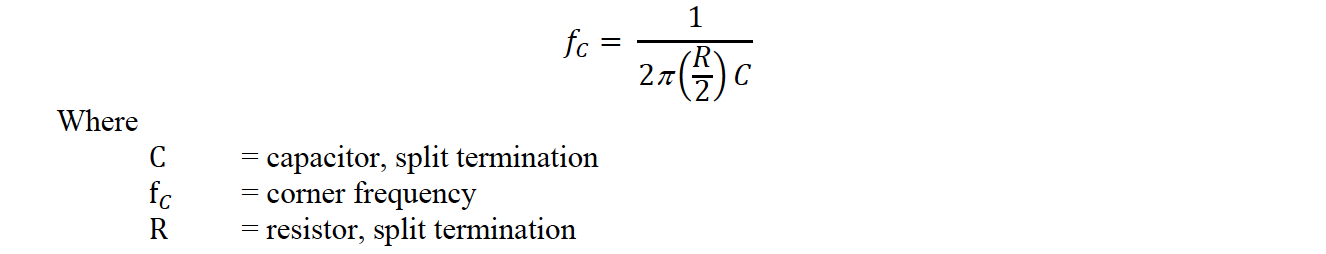

(2)将终端视为一个CM噪声低通滤波器,拐角频率计算如下:

例如,如果R =额定值50Ω,C = 0.1μF,那么拐角频率为≈64 kHz,通常应该足够低。

在CAN(控制器区域网络)应用中使用这种终端的类似版本来提供特殊的SPLIT CM电压偏置而不是GND。

正如最初的知识库文章中指出的,许多SOC和FPGA支持内部差分端接。但是,他们通常不支持CM终止或给予pin访问来支持中心点击。(以上引用的CAN收发器例子是例外)。因此,如果CM噪声是个问题,最好是尽可能禁用内部终端,而使用更高性能的外部差分分离终端。

相关阅读:

秒懂时钟: 抖动衰减时钟设计与应用技巧 – Part 1

秒懂时钟-抖动衰减时钟设计与应用技巧 – Part 2

秒懂时钟-抖动衰减时钟设计与应用技巧 – Part 3 : Clocktoberfest

本文转载自: SiliconLabs

转载地址:http://mp.weixin.qq.com/s/LGHSXMH1x8rXoZo-G-KiQw

声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有,如涉及侵权,请联系小编进行处理。