PCB设计阻抗不连续怎么办?别慌,看这里

cathy -- 周四, 10/15/2020 - 17:15

先来澄清几个概念,我们经常会看到阻抗、特性阻抗、瞬时阻抗。严格来讲,他们是有区别的,但是万变不离其宗,它们仍然是阻抗的基本定义:

a)将传输线始端的输入阻抗简称为阻抗;

b)将信号随时遇到的及时阻抗称为瞬时阻抗;

c)如果传输线具有恒定不变的瞬时阻抗,就称之为传输线的特性阻抗。

先来澄清几个概念,我们经常会看到阻抗、特性阻抗、瞬时阻抗。严格来讲,他们是有区别的,但是万变不离其宗,它们仍然是阻抗的基本定义:

a)将传输线始端的输入阻抗简称为阻抗;

b)将信号随时遇到的及时阻抗称为瞬时阻抗;

c)如果传输线具有恒定不变的瞬时阻抗,就称之为传输线的特性阻抗。

公众号:高速先生(作者:黄刚)

在硬件工程师和PCB工程师的潜意识里,只要是PCB走线阻抗出现了偏差,第一时间就会去和板厂的朋友们去喝喝茶聊聊天。这个时候高速先生悄悄的告诉你们,在对板厂的阻抗加工提出质疑之前,有没有稍微想过一下下有可能是设计的问题呢?

一般来说,单纯PCB走线的阻抗控制出了问题,的确十有八九是由于板厂对加工管控或者参数调整出现偏差,导致加工出来的走线超过了误差范围。因为板厂的确需要对走线阻抗进行一定范围的保证,例如±10%甚至±8%。高速先生一度也是这么认为,直到遇到了下面这个由客户自己进行PCB设计然后我司来制板的项目…

今年的某一天,我们一个客户拿着我们加工的板子过来,就开始抱怨说我们板厂加工的阻抗超过了10%的偏差。50欧姆的表层走线他们自己进行阻抗测试时,发现最低的地方只有44欧姆。还给出了他们的“证据”,也就是实测的阻抗结果。

在进行PCB布线时,经常会发生这样的情况:走线通过某一区域时,由于该区域布线空间有限,不得不使用更细的线条,通过这一区域后,线条再恢复原来的宽度。走线宽度变化会引起阻抗变化,因此发生反射,对信号产生影响。

那么什么情况下可以忽略这一影响,又在什么情况下我们必须考虑它的影响?

有三个因素和这一影响有关:

1、阻抗变化的大小;

2、信号上升时间;

3、窄线条上信号的时延。

首先讨论阻抗变化的大小,很多电路的设计要求反射噪声小于电压摆幅的5%(这和信号上的噪声预算有关),根据反射系数公式:

可以计算出阻抗大致的变化率要求为:△Z/Z1≤10%你可能知道,电路板上阻抗的典型指标为+/-10%,根本原因就在这。

阻抗匹配

阻抗匹配是指信号源或者传输线跟负载之间的一种合适的搭配方式。

根据接入方式阻抗匹配有串行和并行两种方式;根据信号源频率阻抗匹配可分为低频和高频两种。

在高速PCB设计流程里,叠层设计和阻抗计算是登顶的第一梯。阻抗计算方法很成熟,不同软件的计算差别不大,相对而言比较繁琐,阻抗计算和工艺制程之间的一些"权衡的艺术",主要是为了达到我们阻抗管控目的的同时,也能保证工艺加工的方便,以及尽量降低加工成本。

计流

作者:Gustavo.Castro

需要测量阻抗(电路中电压和电流之间的关系)的应用需求持续增加,因此,ADI开发了多款阻抗测量IC,如AD5933和ADuCM350,这些产品获得了广泛的市场认可。然而,这些器件并不能满足所有应用的需求,设计人员仍然面临着使用标准组件设计这种测量能力的挑战。其中一些人面对这些选择和挑战可能会有点无所适从。

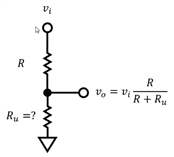

让我们从基础开始,看看现代IC可以做些什么。虽然大多数人都从电压电流比的角度来考虑阻抗,但从电路的角度来说,它可以归结为两个电压信号以及一个已知阻抗和一个未知阻抗之间的关系。例如,要通过未知电阻RU施加电流,我们可以将该电阻放置在具有已知电压vi2和第二个已知电阻R的电路中,这会形成一个分压器,输出电压为vo,可针对RU求解:

本视频将为大家讲解下有关共射放大电路的阻抗与密勒效应的失真的详细内容。

本视频将为大家讲解下有关阻抗与滤波器的详细内容。

随着电子技术的发展,电磁兼容性问题成为电路设计工程师极为关注和棘手的问题。 根据多年的工程经验,大家普遍认为电磁兼容性标准中最重要的也是最难解决的两个项目就是传导发射和辐射发射。为了满足传导发射限制的要求,通常使用电磁干扰(EMI)滤波器来抑制电子产品产生的传导噪声。但是怎么选择一个现有的滤波器或者设计一个能满足需要的滤波器?工程师表现得很盲目,只有凭借经验作尝试。

要想保持印制电路板信号完整性,就应该采用能使印制线阻抗得到精确匹配的层间互连(通孔)这样一种独特方法。 随着数据通信速度提高到3Gbps以上,信号完整性对于数据传输的顺利进行至关重要。电路板设计人员试图消除高速信号路径上的每一个阻抗失配,因为这些阻抗失配

要想保持印制电路板信号完整性,就应该采用能使印制线阻抗得到精确匹配的层间互连(通孔)这样一种独特方法。