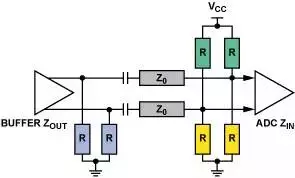

时钟信号衰减会增加抖动,因此对驱动器输出的端接很重要。为了避免抖动和时钟质量降低的不利影响,需要使用恰当的信号端接方法。这里和大家分享4种端接方法。

● Z0是传输线的阻抗;

● ZOUT是驱动器的输出阻抗,

● ZIN是接收器的输入阻抗。

PS:这里仅显示CMOS和PECL/LVPECL电路。

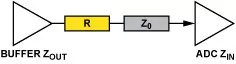

串行端接

实际上,因为阻抗会随频率动态变化,难以达到阻抗匹配,所以缓冲器输出端可以省去电阻(R)。

优势:

● 低功耗解决方案(没有对地的吸电流)

● 很容易计算R的值R(Z0–ZOUT)

弱点:

● 上升/下降时间受RC电路的影响,增加抖动

● 只对低频信号有效

备注:

● CMOS驱动器

● 不适合高频时钟CMOS drivers信号

● 适合低频时钟信号和非常短的走线

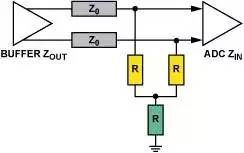

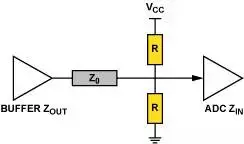

下拉电阻

CMOS

优势:非常简单(R=Z0)

弱点:高功耗

备注:不推荐

LVPECL

优势:

● 简单的3电阻解决方案。

● 就节能而言稍好一点,相对于4电阻端接来说节省一个电阻。

备注:推荐。端接电阻尽可能靠近PECL接收器放置。

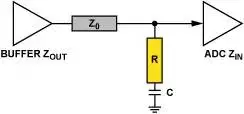

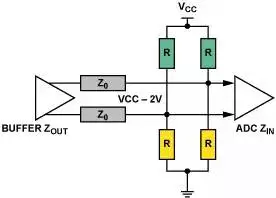

交流端接

CMOS

优势:没有直流功耗。

备注:为避免较高功耗,C应该很小,但也不能太小而导致吸电流。

LVPECL

优势:交流耦合允许调整偏置电压。避免电路两端之间的能量流动。

弱点:交流耦合只推荐用于平衡信号(50%占空比的时钟信号)。

备注:交流耦合电容的ESR值和容值应该很低。

电阻桥

CMOS

优势:功耗实现合理的权衡取舍。

弱点:单端时钟用两个器件。

LVPECL

弱点:差分输出逻辑用4个外部器件。

备注:3.3V LVPECL驱动器广泛应用端接。

本文转载自:亚德诺半导体

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理。