上一次我们分享了一篇内容,主要讲述了差分电路的4大优点,今天我们就说说差分滤波器布局时需要考虑哪些方面?

1、成对差分走线的长度须相同。此规则源自这一事实:差分接收器检测正负信号跨过彼此的点,即交越点。因此,信号须同时到达接收器才能正常工作。

2、差分对内的走线布线须彼此靠近。如果一对中的相邻线路之间的距离大于电介质厚度的2倍,则其间的耦合会很小。此规则也是基于差分信号大小相等但方向相反这一事实,如果外部噪声同等地干扰两个信号,则其影响会互相抵消。同样,如果走线并排布线,则差分信号在相邻导线中引起的任何干扰噪声都会被抵消。

3、同一差分对内的走线间距在全长范围内须保持不变。如果差分走线彼此靠近布线,将影响总阻抗。如果此间距在驱动器与接收器之间变化不定,则一路上会存在阻抗不匹配,导致反射。

4、差分对之间的间距应较宽,以使其间的串扰最小。

5、如果在同一层上使用铜皮铺地,应加大从差分走线到铜皮铺地之间的间隙。推荐最小间隙为走线宽度的3倍。

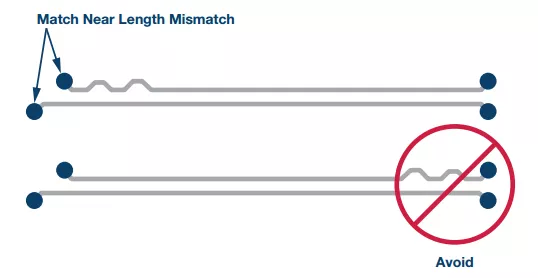

6、在靠近差分对内偏斜源处引入少量弯弯曲曲的校正,从而降低这种偏斜(参见图1)。

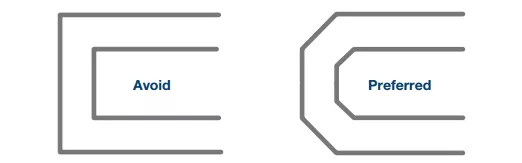

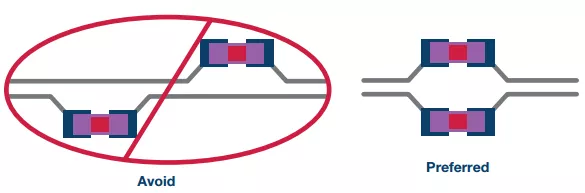

7、差分对布线时,应避免急转弯(90°)(参见图2),应使用对称布线(参见图3)。

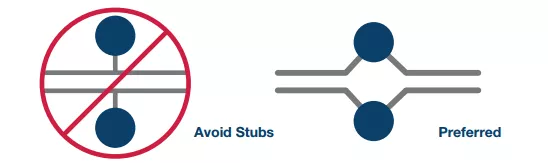

若需要测试点,应避免引入走线分支,而且测试点应对称放置(参见图4)。

8、就降低对滤波器元件值的要求,减少印刷电路板(PCB)上的调谐工作量而言,寄生电容和电感应尽可能小。

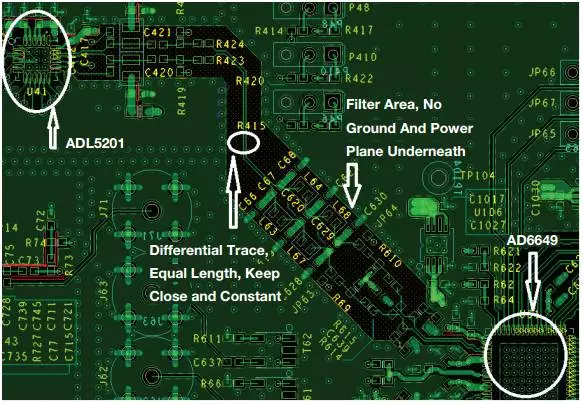

与滤波器设计中的电感设计值相比,寄生电感可能微不足道。寄生电容对差分IF滤波器更为重要。IF滤波器设计中的电容只有几pF。如果寄生电容达到数十分之一pF,滤波器响应就会受到相当大的影响。为了防止寄生电容影响,一个良好的做法是避免差分布线区域和电源扼流圈下有任何接地或电源层。

接收器参考设计板(参见图5)提供了差分滤波器PCB布局的一个示例,如图所示ADL5201和AD6649之间有一个五阶滤波器。AD6649是一款14位250MHz流水线式ADC,具有非常好的SNR性能。

本文转载自:亚德诺半导体

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理。