嵌入式系统正经历重大转型:从物理隔离的自动设备到连接互联网的可访问设备。设计人员了解到,转变的要求远不止将网络接口连接至总线以及添加一个互联网协议堆栈,这令他们非常沮丧。在许多方面,这些互联网感知设计更像小型企业数据中心,而非传统的嵌入式系统。

多项数据中心技术(如多任务处理、多处理和快速专用网络)已经为大型嵌入式系统设计人员所熟知,尽管规模要小很多。但是系统安全性可能是一项新数据中心技术。一旦您将嵌入式系统连接互联网,塑造数据中心安全架构的需求神奇地出现了。不同于计算、存储或连接要求,当您将系统从仓库大小的数据中心缩小为互联的嵌入式设备时,安全需求不会大幅减少。

数据中心安全性

那么,数据中心和互联的嵌入式系统在安全性方面有何需求?首先,它们需要保护自己免遭外部攻击和自身应用的内部破坏。这意味着提供一个受保护的范围,在该范围内,对于任何读取或写入代码或数据的尝试,都将在执行前进行验证。这也意味着在可信范围之外,用于操作系统、管理程序、管理或维护的所有系统代码和数据都必须在存储或传输时进行强加密。

其次,数据中心必须支持其应用的安全需求。应用可能为它们的客户提供传输层安全性(TLS,之前被称作安全套接层或 SSL),它们也可以使用公共密钥验证和加密。它们可能需要经过验证和加密的进程间通信和存储,通常使用对称密钥加密。它们将通过数据中心进行密钥管理,通常是加密算法加速。

上述所有需求均包含 3 个相同的元素。它们均需要一个安全、加速的环境(图 1),用于执行加密算法。它们需要以安全的方式创建、存储、发送和接收加密密钥。为了创建不易破解的密钥,它们需要一个基于物理熵源的真正的随机数生成器。

加密算法需要一个特殊环境,原因有以下两点:首先,必须保证它们的安全,使其免受损坏与监控。它们是数据中心内的理想攻击点。其次,它们可能对应用 CPU 造成无法忍受的计算负担,增加延迟敏感等级最高的应用环境中的延迟。这两点使人联想到物理安全专用硬件加速器。

加密密钥管理带来了类似的问题。显然,机密密钥必须保密。需要注意的是,必须保护公共密钥免受篡改的影响。如果黑客可以用她创建的密钥来替换您从认证中心获取的公共密钥,您将验证来自黑客的消息,而不是真正的消息。这些顾虑阻止未加密密钥位于服务器内存或存储中。事实上,一些专家甚至宣称不允许加密密钥位于共享内存中。

随机数问题更数学化。为了生成新密钥,您需要从随机数入手。如果数字不是真正的随机数,但是遵循了某种统计模式,那么您缩小了攻击者的搜索范围,这是他们发现密钥的必要步骤。但是,软件随机数生成器只是近似于真正的随机分布。近似值越不准确,攻击者就越容易通过定向试错发现密钥。因此,在理想情况下,您应该通过采样真正的随机物理流程来获得随机数,如延迟线抖动、RF 噪音或半导体接点噪音。我们迫切需要一款基于硬件的随机数生成器。

HSM

这些因素促使厂商开发了一款名为硬件安全模块 (HSM) 的专用设备,并且安装于多数数据中心内。无论是主板还是盒子外形,HSM 均满足了上面列出的要求,还提供了多个独特特性。

首先,HSM 具有物理防篡改性,其原理与智能卡基本相同。封装经过专门设计,可抵抗渗透、电压调节、热侵蚀,甚至 X 射线或离子束检查。这些事件将触发模块删除内部内存。在理想情况下,模块还应阻止侧信道攻击,如差分功耗分析。

其次,HSM 应提供面向加密算法加速、密钥存储和随机数生成的专用硬件。

第三,HSM 必须拥有异常严格的防弹防火墙。设备应仅回应经过验证的请求,面向几个预定义动作,如加密与解密字符串或创建、读取、写入或应用密钥。私有或机密密钥只能在严格的条件下以加密的形式读取。必须对两个特殊功能、密钥备份与恢复(通常在智能卡中)和固件更新进行精细控制,最好通过至少一个可信的人实施多方身份验证。

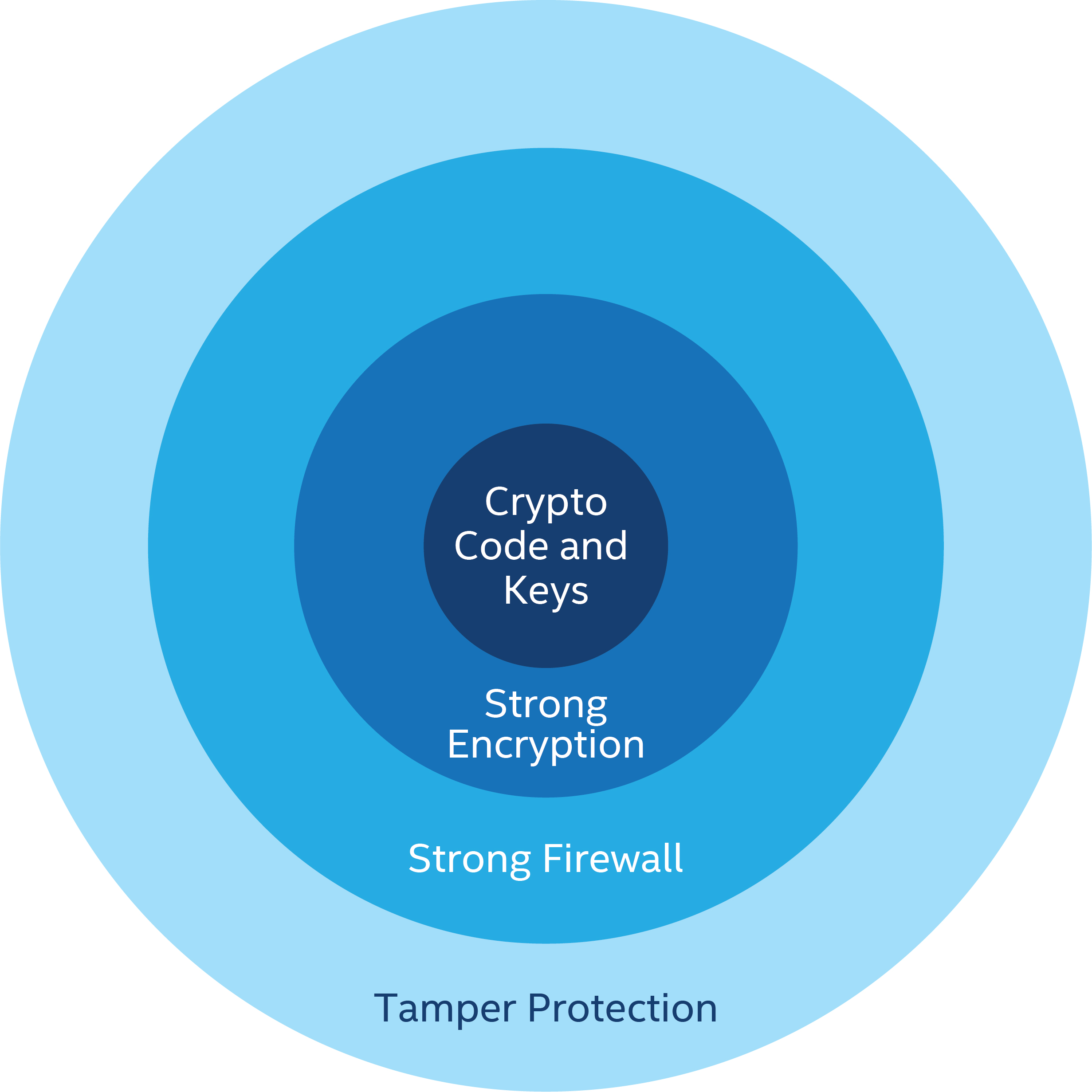

由于提供了多个层面的安全性,从外部篡改防护到内部数据和代码的强加密,HSM 变得非常难以攻击,对于多数攻击者,不值得费如此大的周折(图 2)。遗憾的是,在实践中,通常因为数据中心的其他部分更为薄弱,所以才不值得大费周章。无论如何,HSM 为其他数据中心安全架构的构建奠定了基础。

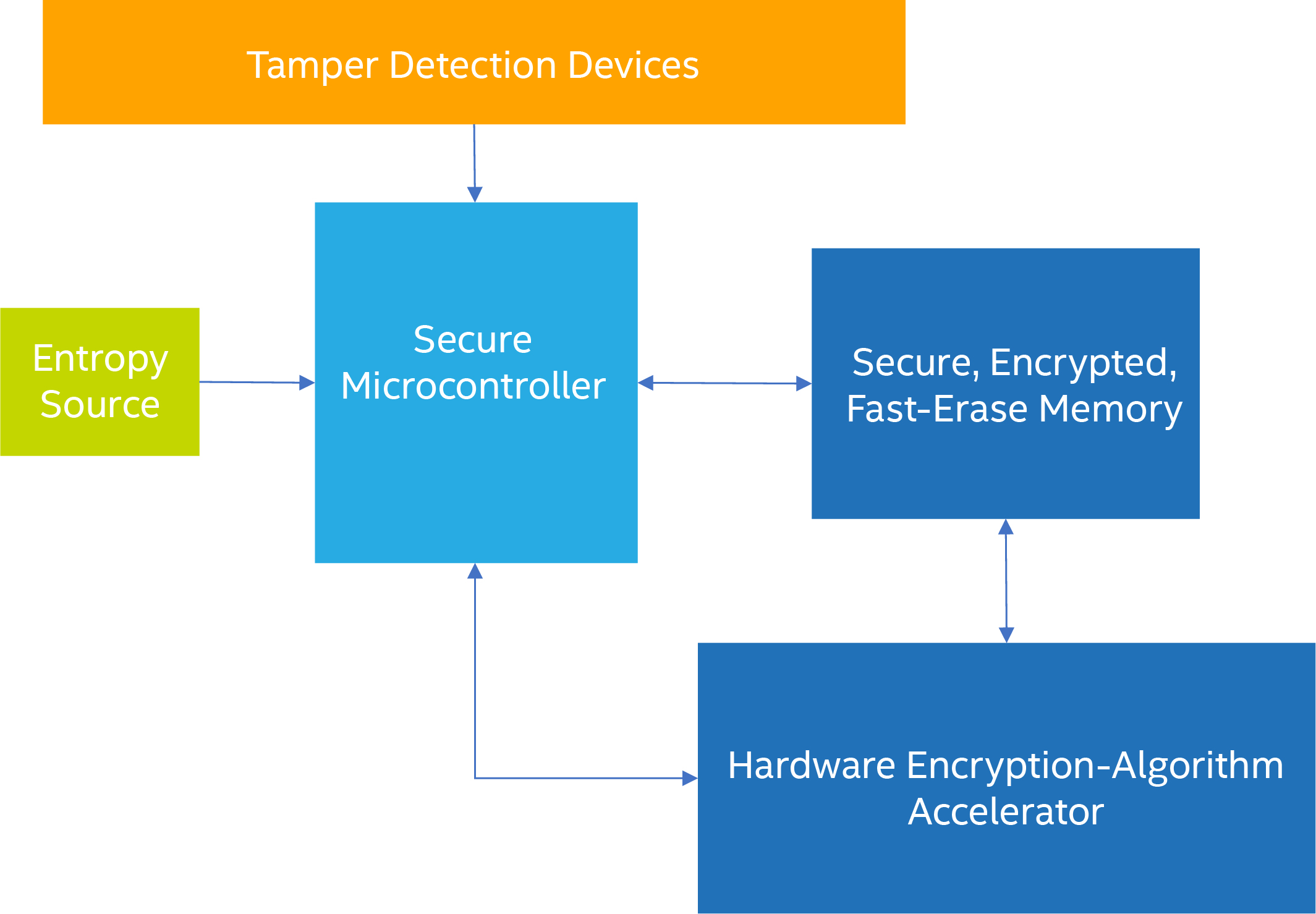

我们可以理解 HSM 厂商对描述模块架构不感兴趣。但是可以概括一下典型的箱式 HSM 包含什么内容(图 3)。

防篡改功能需要硬件支持,包括运动、电容、辐射、电压和温度传感器。将有一个安全的微控制器,在理想情况下,内存和 I/O 接口上配备了内嵌加密/解密。该 MCU 负责监控传感器以及监督 HSM 的其他功能。它还负责读取某种模拟设备,以获取随机数生成的种子。当然,MCU 应该能够免受侧信道攻击。

此外,应该有一个用于密钥存储的安全内存。在理想情况下,它应该是一个能够抵抗外部扫描的自定义设备,检测到入侵后可立即擦除。但是,由于密钥存储需要大量内存,在数据中心内执行加密与解密任务需要大量缓冲区,因此,DRAM 成为了唯一可行的解决方案,安全特性必须集成至 DIMM。

由于防火墙具有较高的限制性,它可以在硬件状态机内实施,减少 MCU 的成本,并降低 MCU 软件遭受攻击的风险。最后,我们的 HSM 将包括一个加密算法加速器。这通常是一个针对必要的加密和身份验证算法优化的硬件数据路径。

最后的语句存在问题。数十款密钥交换、身份验证和加密算法得到了广泛应用。墨菲定律规定数据中心必须支持它们的大型子集,以及应用开发人员设想的某些专有算法。使用固定的硬件加速器满足所有需求意味着只加速非常基本的运算,如同在大型乘法累加器库中,然后将大量工作移回 MCU,或者构建一个非常复杂、非常难以验证的可重新编程状态机。如果采取第二种方法,数据中心经理将立即施加压力,以增强加速器的通用性和用户可访问性,加速应用。HSM 厂商必须考虑这些需求,也应了解确保加速器在设计过程中的可验证性和运算期间的安全性是绝对必要的。尽管某些安全专家指出,用户可编程性和安全性完全不兼容。如果您想使加速器免受损坏,必须在设计阶段定义并验证它的功能。

自定义硬件(主要是加密数据路径)可以在简单的 ASIC 中完成,但是需要特别注意以确保差分功耗攻击不会收集来自 ASIC 电源轨的任何信息,并且电路能够免受电压和温度漏洞的影响,这无异于设计智能卡芯片时采取的防范措施。借助这些配置,如果设计团队拥有必要的专业知识或访问相应知识产权 (IP) 的权限,安全的 MCU 内核也可以被添加至 ASIC。例如,ARM 目前正提供一种基于 Cortex*-M 架构的防篡改处理器 IP 核系列,并将其命名为 SecureCore。如果繁重的加密算法停留在加速器中,这样做就足够了。

也可以在 FPGA 中完成自定义设计。但是使用 FPGA 会带来新的问题。多数 FPGA 为易失性,并且在通电时从外部内存对其配置。这个启动流程可以受加密的保护,厂商提供了加密功能。此外,多数 FPGA 拥有有限的混合信号功能或不具备该功能。因此,无法集成篡改检测所需的传感器输入范围,不包含外部模数转换器 (ADC),它本身会扩大攻击面,需要保护。对外部配置 ROM 的需求和混合信号电路的缺乏也有例外情况,但是一般是小型设备,如英特尔® MAX® 10 设备产品家族。

FPGA 还带来了新的机会。由于加速器数据路径支持运行时重配置,可以按需针对每个算法家族重新配置加密加速器,绕过灵活性与安全性的难题。还需在 FPGA 中创建熵源,以供真正的随机数生成器使用。

所有这些实施选项引发了另一个重要问题。面对多种 HSM 实施方式,用户如何了解特定设备的安全性如何?答案是独立认证。HSM 使用的主要标准 – 联邦信息处理标准(FIPS) 140-2 由美国国家标准与技术研究院 (NIST) 创立。FIPS 140-2 定义了 4 个安全级别,从弱端上未受保护的密码引擎到因入侵而完全封闭的引擎与存储子系统以及防篡改或检测强端上的硬件。每个设计都必须经过第三方实验室的认证,该实验室得到了 NIST 和加拿大通信安全部共同执行的认证计划的认可。

也可以根据国际信息技术安全评估通用准则(简称为 CC)ISO 15408 在产品层面上对 HSM 进行评估。该认证流程同样由公认的第三方实验室实施。但是不同于评估 HSM 总体实际安全级别的 FIPS 140-2,CC 评估实际上只检查是否支持厂商提交的请求。该方法可能包括也可能不包括产品的实际测试,例如,它用于使各种 Microsoft Windows 版本通过 CC 认证。用户可以确定实际上认证了什么、在什么级别以及对自己的用例造成了哪些影响。

嵌入式 HSM?

将 HSM 引入数据中心的挑战目前体现在边缘计算,存在几个重要差异。相比数据中心面临的海量算法,嵌入式系统可能仅使用几个加密算法。同样地,相比数据中心,互联的嵌入式系统可能需要管理更少的密钥。这两个差异可以简化将 HSM 引入嵌入式系统的一个大问题,

即规模问题。根据功能和安全级别的不同,数据中心 HSM 的花费从几百美元到几千美元不等。尺寸也涵盖了从 PCIe* 卡到披萨盒子的大小。对于摆满服务器的边缘计算机架,这不是一个严重的问题。但是对于装入小盒子或机械组合电路板的典型嵌入式系统,这是不可能实现的。用户向 HSM 技术提出了明确的要求,从披萨盒子缩小为芯片级,同时不影响功能或安全性。

但是这可行吗?从技术上来说,答案似乎是肯定的。我们发现,HSM 的所有功能在理论上都能集成至 ASIC 或 FPGA,某些传感器和物理入侵检测的机械元件除外。MCU 厂商已经提供了完整解决方案的部件,包括安全软件执行模式、片上私有内存和受限的加密加速器。一份报告指出,即使普通的智能卡硬件也能用作相当安全但是受限的 HSM。因此,掌握必要技能、有抱负的嵌入式设计团队应该能够生产出芯片级 HSM。

但是这样的项目将面临几个严峻的挑战。必要技能包括安全的处理器和内存设计,对加密的充分了解和物理篡改防护方面的经验。但是在嵌入式设计团队中,这种技能组合并不常见。设计应获得 FIPS 140-2 认证。但是这是一个昂贵与耗时的过程,如同 ISO 15408,动辄需要数十万美元和几个月的延迟。上述所有工作只能分摊至设计阶段相对少量的嵌入式系统中。

说服管理人员注重系统安全性,忽略折中措施,以及进行 HSM 芯片设计是最严峻的挑战,也许是不太具体的挑战。遗憾的是,管理人员对互联嵌入式系统所面临的威胁仍抱有不切实际的想法,即便对于面临巨大损坏风险的发电和运输等应用。

但是还有其他方法。如今,市场更加广阔,专业知识更容易获得,这也许是半导体厂商创建经过 FIPS 140-2 认证的 HSM 芯片的最佳时机。在某种程度上,脆弱又重要的实体工厂经历了几次备受瞩目的攻击之后,边缘计算的进一步发展可能需要它。

本文转载自:Altera - SDJ

声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有,如涉及侵权,请联系小编邮箱:cathy@eetrend.com 进行处理。