ADI 在其许多时钟和定时产品中采用了数字锁相环 (DPLL) 技术。除了频率转换灵活性以外,DPLL 技术还能提供多种对系统有用的数字功能,例如:时钟验证、相位或频率可控的切换、 精准平稳地进入和退出保持模式。

本文将探讨如何使用 DPLL实现相位增建和无中断切换。

相位增建和无中断有两类切换。这两类切换没有通用定义,本问给出如下定义:

● 相位增建(buildout)是指将切换时间增建到 DPLL 中时, 两个参考之间的相位差。此相位差是输出与锁定的有 效参考之间的相移。

● 无中断与零延迟类似,获取相位锁定后,输出相位跟 随有效参考相位。 有关从参考 A 切换到参考 B 的无中断和相位增建切换操作的更多信息,请斟酌“同频切换”部分和“异频切换”部分中的示例。

同频切换

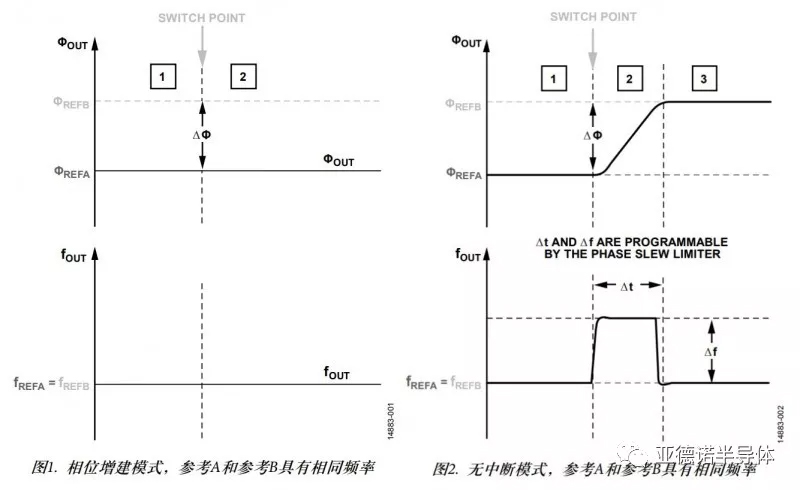

在图 1 和图 2 中,参考 A 和参考 B 具有相同的频率和相移 ΔΦ。

相位增建模式——同频

区间 1

参考 A 有效。DPLL 的相位和频率均锁定参考 A。假定无相 移,ΦOUT = ΦREFA,fOUT = fREFA。ΦOUT为输出相位,fOUT为输 出频率。

切换点:参考 B 变为有效。参考 A 和参考 B 之间的相移 ΔΦ 作为偏移增 建到 DPLL的鉴频鉴相器 (PFD) 中。

区间 2

DPLL 随后锁定参考 B,ΦOUT = ΦREFA,fOUT = fREFA = fREFB。输出和有效参考 B 之间存在一个固定相移 ΔΦ。固定相移是相位增建的典型特性。

无中断模式——同频

区间 1

参考 A 有效。DPLL 的相位和频率均锁定参考 A。假定无相 移,ΦOUT = ΦREFA,fOUT = fREFA。

切换点:参考 B 变为有效。参考之间的相位差为 ΔΦ。

区间 2

DPLL 将输出相位从 ΦREFA 扭转到 ΦREFB。在此锁定时间(Δt) 转换期间,有一个频率偏移 Δf,其与 Δt 成反比,也就是说锁定时间越短,频率偏移越大。对于 ADI 公司的 DPLL 时钟 产品,设置相位压摆率可控制锁定时间和频率偏移。

区间 3

DPLL 随后锁定参考 B,ΦOUT = ΦREFA,fOUT = fREFB。对于无中断切换,输出与有效参考之间无相移。

异频切换

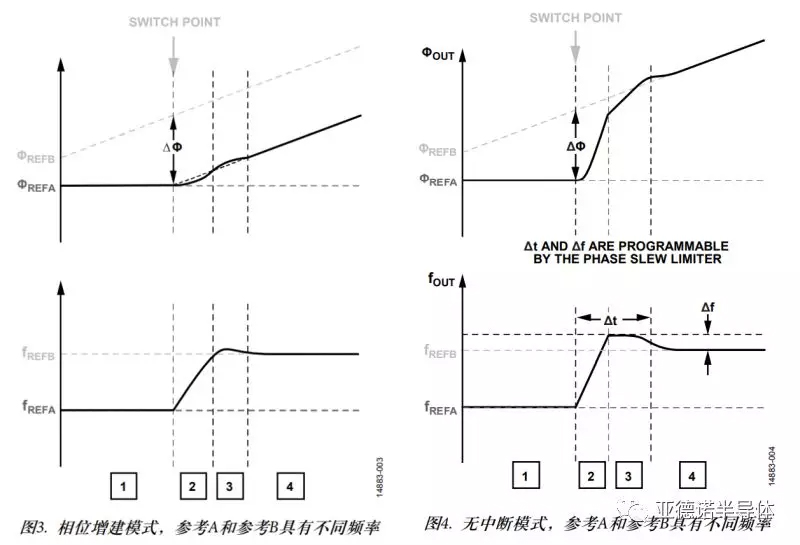

在图3和图4中,参考 A 和参考 B 具有不同的频率。

相位增建模式——异频

区间 1

参考 A 有效。DPLL 的相位和频率均锁定参考 A。假定无相移,ΦOUT = ΦREFA,fOUT = fREFA。

切换点:参考 B 变为有效。在此切换点,参考之间的相位差为 ΔΦ。

区间 2

DPLL 试图获取频率锁定。在切换点,参考之间的相位差 ΔΦ 增建到DPLL的 PFD 中。在此期间,系统的相位和频率均解除锁定。

区间 3

DPLL的频率锁定参考 B,相位正在以 ΔΦ 的增建相移锁定参考 B。在区间 2 和区间 3 中,锁定时间和频率偏移均是自行管理。这种情况下,相位压摆限幅器对 Δt 和 Δf 无影响。

区间 4

DPLL 的相位和频率均锁定参考 B,ΦOUT = ΦREFB − ΔΦ,fOUT= fREFB。输出和有效参考 B 之间存在一个固定相移 ΔΦ,表示这是相位增建模式。

无中断模式——异频

区间 1

参考 A 有效。DPLL 的相位和频率均锁定参考 A。假定无相移,ΦOUT = ΦREFA,fOUT = fREFA。

切换点:参考 B 变为有效。参考之间的相移为 ΔΦ。

区间 2

DPLL 试图获取频率锁定。在此期间,系统的相位和频率均解除锁定。相位压摆限幅器在此期间有效,以便管理锁定时间和频率偏移。

区间 3

DPLL 的频率已锁定参考 B,相位正在锁定参考 B。相位压摆限幅器在此期间同样有效,以便管理锁定时间和频率偏移。

区间 4

DPLL 的相位和频率均锁定参考 B,ΦOUT = ΦREFB,fOUT = fREFB。

本文转载自:亚德诺半导体

声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有,如涉及侵权,请联系小编邮箱:cathy@eetrend.com 进行处理。