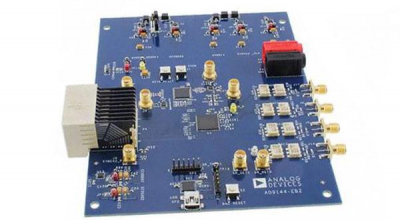

高速PCB设计绕等长一定要绕个山路十八弯才算牛?

cathy -- 周二, 01/09/2018 - 10:26

初次接触高速讯号或DDR设计的人,可以找到一些在谈走线绕等长的 旧资料(当中不乏过去大厂的design guide),但近几年一些DDRII(或更快)的design rule,渐渐改以定义setup time, hold time budget with jitter取代length-matching routing rule,并且改以强调对时序图的理解与使用模拟(margin predic