1、首先给出异步复位信号亚稳态的原因:

复位结束也就是释放的时刻恰在时钟上升沿的建立时间和保持时间之间时无法决定现在的复位状态是1还是0,造成亚稳态。

下面是具体解释:

在带有复位端的D触发器中,当reset信号“复位”有效时,它可以直接驱动最后一级的与非门,令Q端“异步”置位为“1”or“0”。这就是异步复位。当这个复位信号release时,Q的输出由前一级的内部输出决定。

然而,由于复位信号不仅直接作用于最后一级门,而且也会做为前级电路的一个输入信号,因此这个前一级的内部输出也受到复位信号的影响。前一级的内部电路实际上是实现了一个“保持”的功能,即在时钟沿跳变附近锁住当时的输入值,使得在时钟变为高电平时不再受输入信号的影响。对于这一个“维持”电路,在时钟沿变化附近,如果“reset”信号有效,那么,就会锁存住“reset”的值;如果reset信号释放,那么这个“维持”电路会去锁当时的D输入端的数据。因此,如果reset信号的“释放”发生在靠时钟沿很近的时间点,那么这个“维持”电路就可能既没有足够时间“维持”住reset值,也没有足够时间“维持”住D输入端的值,因此造成亚稳态,并通过最后一级与非门传到Q端输出。如果reset信号的“释放”时间能够晚一点点,也就是说,让“维持”电路有足够的时间去锁住“reset”的值,那么,我们就可以肯定输出为稳定的“reset”状态了。这一小段锁住“reset”值所需要的时间,就是寄存器的removal time要求。

2、如果上面的没有看懂,那么下面的解释得比较清楚。

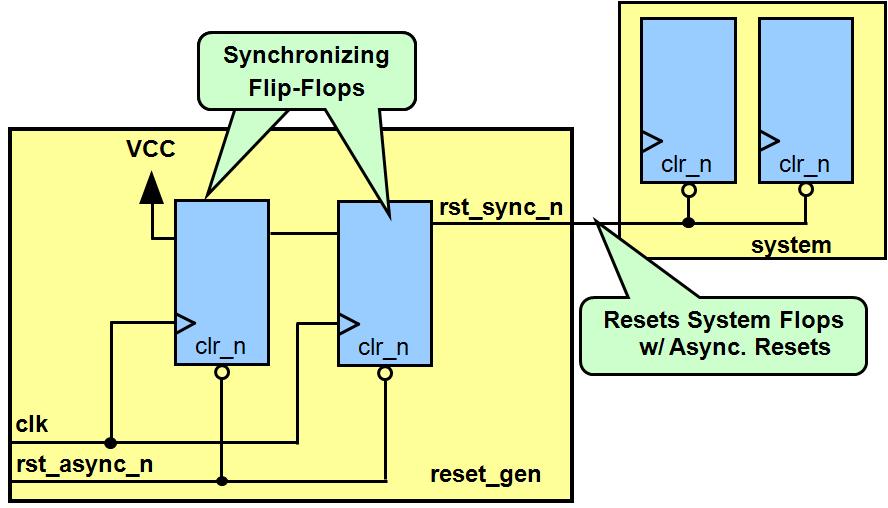

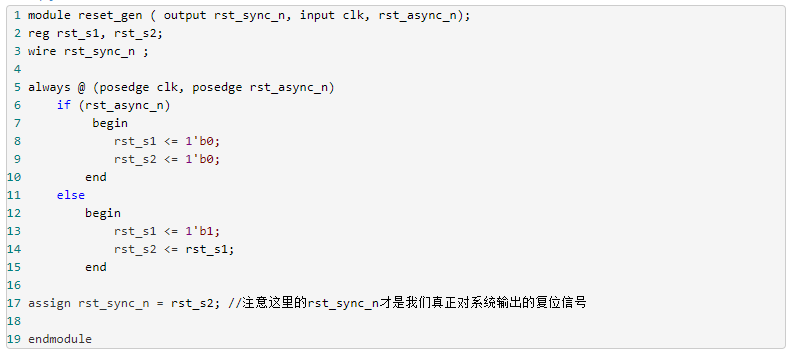

如图第一个方框内是异步复位和同步释放电路。有两个D触发器构成。第一级D触发器的输入时VCC,第二级触发器输出是可以异步复位,同步释放后的复位信号。

1)电路目的:防止复位信号撤除时产生亚稳态事件。

2)什么是异步复位和同步释放:是指复位信号是异步有效的,即复位的发生与clk无关。后半句“同步释放”是指复位信号的撤除也与clk无关,但是复位信号是在下一个clk来到后起的作用(释放)。

下面说明一下如何实现异步复位和同步释放的。

异步复位:显而易见,rst_async_n异步复位后,rst_sync_n将拉低,即实现异步复位。

同步释放:这个是关键,看如何实现同步释放,即当复位信号rst_async_n撤除时,由于双缓冲电路(双寄存器)的作用,rst_sync_n复位信号不会随着rst_async_n的撤除而撤除。

假设rst_async_n撤除时发生在clk上升沿,如果不加此电路则可能发生亚稳态事件,但是加上此电路以后,假设第一级D触发器clk上升沿时rst_async_n正好撤除,则D触发器1输出高电平“1”,此时第二级触发器也会更新输出,但是输出值为前一级触发器clk来之前时的Q1输出状态。显然Q1之前为低电平,顾第二级触发器输出保持复位低电平,直到下一个clk来之后,才随着变为高电平。即同步释放。

本文转载自:长弓的坚持的博客

转载地址:http://blog.csdn.net/wordwarwordwar/article/details/74091796

声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有,如涉及侵权,请联系小编进行处理。