近年来,随着电路设计规模和复杂度的不断扩大,需要测试的场景也在成倍的增加,这使得对每一个场景都进行直接测试变得不太可能完成,或者说完成所需要的投入和产出比值太大,所以在数字验证方面引入了新的验证方法学:基于SV和UVM的随机验证,而对于电路规模和复杂度的急剧增大在模拟和混合电路设计方面也存在这样的问题,所以我们在模拟和混合电路设计验证中引进了UVM-MS验证方法,它的思想是从数字验证方面的UVM借鉴而来,里面包含数字模型和随机化这些在数字模块验证中才有的特性,在本篇文章我们将会一起讨论怎么把这些数字化的验证方法应用到模拟验证领域中。

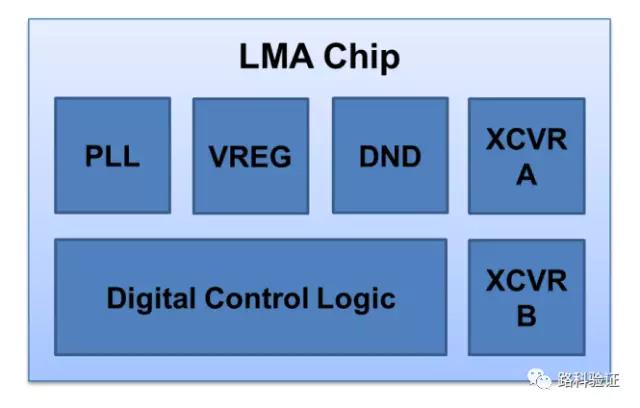

下面我们以一个混合电路模块为例来介绍如何在把随机化的验证方法应用在混合电路设计领域中,下图是我们的混合模块电路结构。

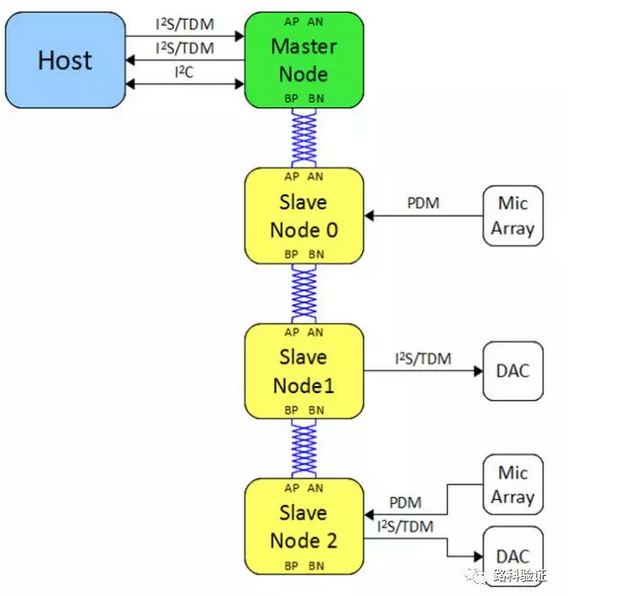

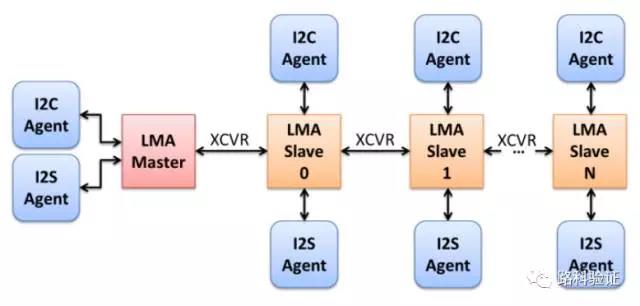

LMA处理器中包含五个模拟模块(PLL,DND,VERG,XCVRA,XCVRB)和一个大型的数字逻辑控制模块(Digital Contral Logic),其中,PLL模块负责为数字逻辑模块和XCVR模块提供时钟,XCVRA和XCVRB模块分别负责发送和接受数据,VERG模块负责为PLL模块,数字逻辑控制模块,DND模块提供不同的供电电压,DND模块负责判断是否具备可以通信的条件,我们的验证点主要包括验证一个LMA是否能正常工作以及LMA被嵌入系统环境中可不可以正常工作,下图展示了一个包含四个节点的LMA系统。

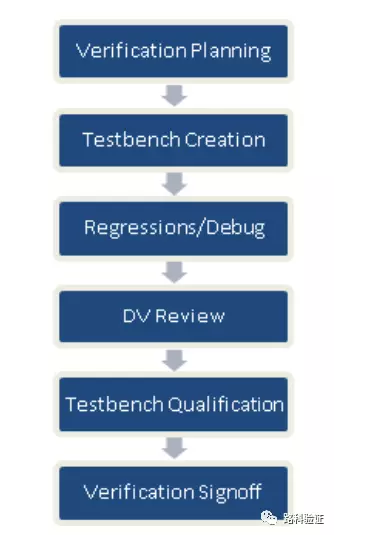

对于这样的混合设计电路来说,在以前的验证方法中,一般是电路设计人员分别验证自己设计的模块,这样他对于需要验证什么功能,芯片怎么样可以正常跑起来以及有哪些变量会影响芯片的性能等等这些问题是非常清楚的,但是存在的一个问题是他们都是自己验证自己的模块,所做的这些验证的测试激励或者方法由于没有统一的验证流程,对于我们项目的验证过程来说是不可见的,而对于数字的验证环境来讲,我们有统一的验证方法,具体流程如下图:

首先我们需要建立验证计划来决定在验证过程中需要验证的场景,根据验证计划来搭建block,chip,system级别的验证平台,它们都是基于SV和UVM的随机化测试平台,可以自己检查测试激励通过与否,然后根据回归测试的结果收集覆盖率信息来检查验证的完备性,最后设计和验证人员进行review来增加验证的信心,下面我们根据这些标准流程来看看怎么把这套数字化的验证方法应用到混合电路设计的验证过程中来。

一、验证计划

对模拟或者混合电路设计的验证过程中存在的最大问题是你没有任何文档可以去参考之前它们是如何被验证和测试的,除非你找到当初设计和验证这个模块的人,验证完成后测试平台并不会被版本管理工具进行保留,而且即使保留了,你也不能确定那是不是正确的版本,我们要做的第一件事就是把这些验证的流程在版本管理工具中正确的留下来,以防我们每次验证都要从头做起,接下来我们通过两步来创建LMA芯片的验证计划,第一步是找到数字设计工程师,模拟设计工程师,验证工程师一起来解决下面的几个问题:

1、LMA芯片成功工作的表现以及怎么验证它

2、哪些block对于LMA芯片的性能影响比较大?它们是否需要block级别的验证平台

3、由于系统级别的测试都是在基于许多spice模型的基础上进行仿真的,那些模型可以在更高抽象层上面进行模拟以及我们怎么去验证更高抽象层上模拟模型的正确性

经过讨论之后我们确定应该建立五个分开的测试平台:PLL block level,VERG block level,DND block level,LMA system level(里面包含模拟模块模型),LMA system level(里面包含模拟模块的FastSpice模型),之后对于这五个测试测试平台我们都建立了验证计划,然后我们便有了下面的结果:

1、所有需要被配置的输入参数以及他们的合法值

2、所有需要检查的信号自己它们正确的行为

3、需要添加的测试激励

4、功能覆盖率的要求

并且这些验证计划以及验证测试点都被记录在我们的验证网页上,这样项目经理可以随时来检查验证的进度,而且对于下一个项目的验证有了参考

二、回归测试

应用到混合电路设计中最有效的数字技术就是测试激励的自动对比结果这个特性了,在以前的验证过程中我们都是通过手动检查波形来确定测试激励是否通过,当然这也和模拟验证环境的工具有关系,一般来说你很难相信工具是完全可靠的,这种情况对于比较少的测试激励还行得通,但对于回归测试来说却是非常困难,这就导致如果我们修改了一个bug并不能马上测试它有没有引入新的bug,有可能得等到好几周以后才能发现,这就对设计电路埋藏了隐患,而在引入数字电路验证的思想之后,我们在测试激励的仿真过程中加入了一些检查的点,例如电压不能超过6V,电流必须在600uA到800uA之间,然后把这些检查点加入回归测试流程中进行回归测试,它们会导致一些测试激励fail,然后再去debug这些failed的测试激励,有些这些测试点,我们便可以进行大规模的回归测试来验证模拟模块的行为正确性。

三、验证平台

1.模块验证平台(PLL,VREG,DND)

对于PLL模块我们采用基于UVM的验证平台主要是想测试一些仿真过程中产生的抖动,它们对于模拟电路的性能有着比较大的影响,而以我们都是利用基于原理图的测试平台进行仿真的,下面是我们写的检测仿真jitter的UVM monitor代码,它能够轻易的测量CTC和TIE的jitter。

由于电压校准器在设计电路中是十分关键的,我们针对VREG模块搭建了验证平台,它的验证平台是传统的基于电路原理图的设计,仿真也是利用Spice的仿真器进行,虽然验证平台和以前没有区别,但我们针对它建立了一些验证计划以保证所有的特性都可以被测试激励检查到,然后我们根据验证计划写了一些测试激励并加入了自动检查的特性,那些failed的测试激励挑出来进行debug,然后回归测试保证没有引入新的bug。

我们建立的最后一个模块验证平台是针对DND模块的,由于它需要Verilog和Spice的联合仿真,我们没有在模块平台上对它进行控制和性能的验证,它里面包含一个控制PLL运行的状态机,由于PLL的锁定的仿真需要很长的时间,所以我们计划在模块平台上就开始验证,以最大程度的减少后期系统验证的工作量,当然DND的验证平台也是基于电路原理图的设计,我们也增加了一些验证计划,并写了对应了的测试激励,加入了自动对比结果的特性。

2.芯片验证平台

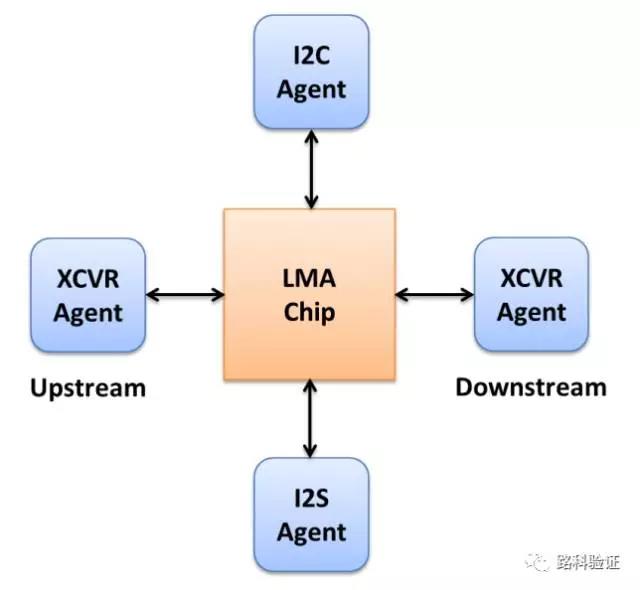

LMA的芯片验证平台是一个例化了LMA设计文件的UVM验证平台,针对芯片中的每一个数字接口都有一个UVC的agent,每一个agent分别包含driver,monitor,sequencer以及一些检查协议的断言和覆盖率代码,具体结构如下图:

3.系统验证平台

系统验证平台是为了验证许多由LMA芯片组成的系统的功能正确性,检查它们是否是通过菊花链的方式接在一起,当然LMA的芯片验证平台中的那些agent和checker仍然可以使用,我们又额外增加了新的计分板来对比结果,平台结构如下图:

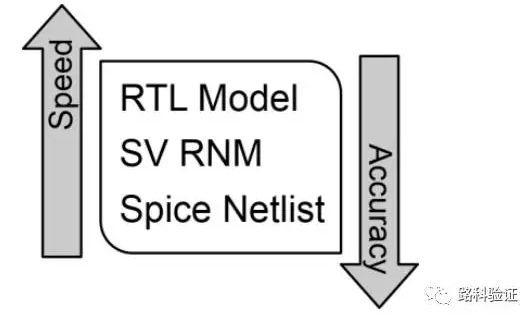

由于系统测试仿真时间比较长,我们在验证环境中做了一些改动,使得它可以同时应用于RTLodel,SV RUM和Spice Netlist不同模型上,这样可以根据仿真需要的精度和时间长短来进行选择仿真模型,这些模型之间的区别如下图:

四、随机化测试

LMA项目是我们应用数字化验证方法在混合电路设计验证中的第一个项目,我们用SV中的real变量类型来模拟一些模拟的模块设计,real变量类型结合SV的随机化特性可以在原来的仿真环境性能上产生一个很大的产出,但是在系统的仿真过程中,由于在Spice仿真器中PLL锁定的时间比较长,我们用一个基于SV的真实的PLL数字模型来代替模拟的PLL模块减少锁定时间,而且在这个模型中我们可以随机化一些必要的参数,如温度,jitter,skew以及电压的设置等等,这样我们可以对系统中每个节点的参数进行随机化的控制,这些在我们以前的spice仿真环境上是没有办法做到的,这样我们就可以大量的去仿真测试激励检查我们有问题或者不达指标的地方,另外在我们原有的spice仿真环境中我们也加入了一些随机化的特性,在DND的基于原理图的仿真环境中的一些电容,我们根据spec把它随机化在1uf到50uf之间,还有片子仿真的corner环境,电压,温度等等都加入了限制范围内随机化的特性,其他详细的随机化特性请参考原文。

五、模拟模块的功能覆盖率

我们在LMA系统中应用的另一个技术是把SV中的功能覆盖率特性引入到模拟模块的验证上,但是功能覆盖率是SV的特性,在我们的Spice仿真环境中并不被支持,为了解决这个问题我们利用了一个后处理的函数来做这件事情,首先Spice仿真器运行过程中把那些随机变量的值打印到spice的log文件中,我们在仿真后期用一个带有SV中功能覆盖率group数据的函数去处理wspice的log文件,这样我们就可以拿到功能覆盖率的信息了,而且这个函数是在每次跑仿真时自动运行的,最终项目的验证结果证明功能覆盖率对于模拟模块的验证是非常有用的,在验证期间发现了几个没有被正常随机化的变量问题。

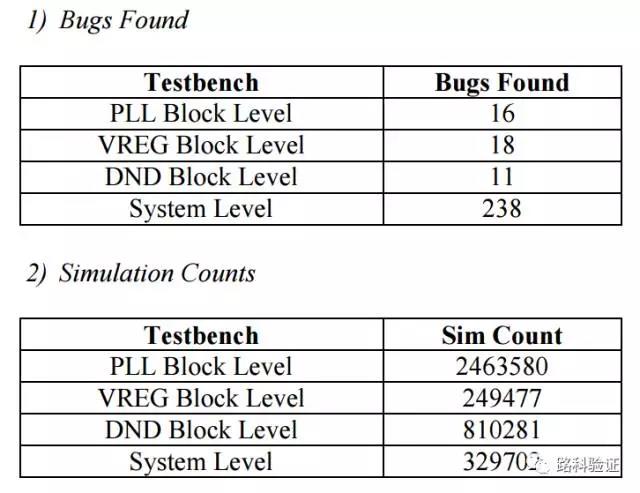

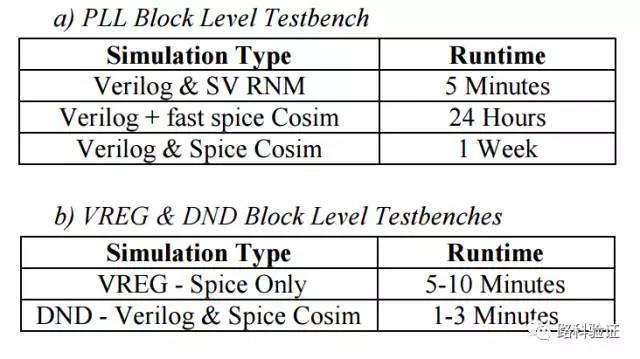

在项目后期由于第一次tapeout之后发现了一些系统级别的bug,我们又在验证过程中加入了基于spice仿真环境的联合仿真,具体过程见原文,下面是我们把数字化验证方法应用在混合电路设计验证中的一些量化的结果(仿真时间,bug发现量):

道路总是曲折的,在把数字化的验证方法应用到混合电路设计的过程中出现了很多问题,但总得来说还是非常有用的,尤其是数字电路验证中追求的自动化思想对我们来说启发是非常大的,以后我们要让这些优秀的验证思想进一步在混合电路验证中发挥更大的作用。

本文转载自路科验证