PCB被板厂做坏了,谁来背锅?

cathy -- 周一, 02/01/2021 - 16:35

不知道同学们做坏过PCB板没有?就是做出来的板子,是不能用的。我是有过的,印象中有两次。为什么同样的错误会多次出现呢?下面就来说下具体情况。

PCB板做坏的过程

这两次大概是这样的,将生产文件发给板厂。回板之后,一看PCB,本来是插件HDMI座子,通孔居然没有钻,直接废掉了。

不知道同学们做坏过PCB板没有?就是做出来的板子,是不能用的。我是有过的,印象中有两次。为什么同样的错误会多次出现呢?下面就来说下具体情况。

PCB板做坏的过程

这两次大概是这样的,将生产文件发给板厂。回板之后,一看PCB,本来是插件HDMI座子,通孔居然没有钻,直接废掉了。

“噪声问题!”——这是每位电路板设计师都会听到的四个字。为了解决噪声问题,往往要花费数小时的时间进行实验室测试,以便揪出元凶,但最终却发现,噪声是由开关电源的布局不当而引起的。解决此类问题可能需要设计新的布局,导致产品延期和开发成本增加。

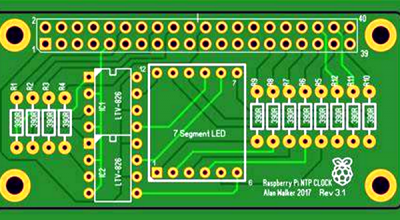

图片

在设计PCB(印制电路板)时,需要考虑的一个最基本的问题就是实现电路要求的功能需要多少个布线层、接地平面和电源平面,而印制电路板的布线层、接地平面和电源平面的层数的确定与电路功能、信号完整性、EMI、EMC、制造成本等要求有关。对于大多数的设计,PCB的性能要求、目标成本、制造技术和系统的复杂程度等因素存在许多相互冲突的要求,PCB的叠层设计通常是在考虑各方面的因素后折中决定的。

1、主要目的

1.1、规范PCB的设计流程。

1.2、保证PCB设计质量和提高设计效率。

1.3、提高PCB设计的可生产性、可测试性、可维护性。

2、适用范围

适用于所有PCB设计人员。

PCB设计,既是科学也是艺术。其中有非常多关于布线线宽、布线叠层、原理图等等相关的技术规范,但当你涉及到PCB设计中具有艺术特质元器件布局问题时,问题就变得有趣起来了。

事实上,关于元器件摆放限制很少,也没有“绝对正确”的规范要求,这也使得初学者电子工程师在摆布电路板上元器件时,就像个十足的“中二”,向往着个人抱负和创造性,如何摆放完全依赖于你和设计思路。

有时候,在设计电路时,需要用到一个阻值比较小的功率电阻作采样电阻,用来采样大电流。很多时候我们都会采用一个大封装的功率电阻来做,例如2010,1812,功率一般0.5W。但是我们有没有想过用PCB走线来设计一个采样电阻呢?下面介绍用PCB走线设计一个0.05欧姆的方法。

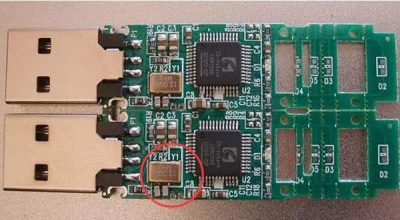

1.贴片之间的间距

PCB上的立碑(tombstone)也叫曼哈顿吊桥或吊桥效应等,是一种片式(无源)元器件组装缺陷状况,其成因是零件两端的锡膏融化时间不一致,而导致片式元件两端受力不均,这种片式元件自身质量比较轻,在应力的作用下就会造成一边翘起,形象的称之为立碑。

也许纯文字描述大家不太好理解,老wu这里分享一份SMT 立碑现象发生过程的视频供大家参考。

在回流前或锡膏熔化前,由于锡膏中凝胶成分的作用,元件两端受到锡膏的粘附力(f)以及本身所受重力(G)的作用而固定在PCB焊盘上,当PCB在轨道上启停时,元件都不会发生移动。

开关电源PCB排版是开发电源产品中的一个重要过程。许多情况下,一个在纸上设计得非常完美的电源可能在初次调试时无法正常工作,原因是该电源的PCB排版存在着许多问题。

引言

晶振有两个比较重要的参数,频偏和温偏,单位都是PPM,通俗说,晶振的标称频率不是一直稳定的,某些环境下晶振频率会有误差,误差越大,电路稳定性越差,甚至电路无法正常工作。

所以在PCB设计时,晶振的layout显得尤其的重要,有如下几点需要注意。

✔ 两个匹配电容尽量靠近晶振摆放。