资料下载:PCB设计秘籍

cathy -- 周日, 06/28/2020 - 15:30

本《PCB设计秘籍》工具书共包含17个章节,按PCB布局布线、散热技巧、接地指导、抗扰度等角度进行分类整理,针对在各种器件、应用环境下,提供一些实用的PCB设计指导以及常见问题解答。

本《PCB设计秘籍》工具书共包含17个章节,按PCB布局布线、散热技巧、接地指导、抗扰度等角度进行分类整理,针对在各种器件、应用环境下,提供一些实用的PCB设计指导以及常见问题解答。

PCB设计的艺术

•好的PCB设计需要花费数十年的时间才能不断磨砺而成

•设计一个可靠的高速,混合系统需要用到大量的理论知识以及与之相对应的实际应用

•这篇文档将会用到许多重要的概念......

电磁兼容性是指电子设备在各种电磁环境中仍能够协调、有效地进行工作的能力。电磁兼容性设计的目的是使电子设备既能抑制各种外来的干扰,使电子设备在特定的电磁环境中能够正常工作,同时又能减少电子设备本身对其它电子设备的电磁干扰。

遵循以下PCB设计技巧,可以有效的提升电路板的电磁兼容性:

一、选择合理的导线宽度

由于瞬变电流在印制线条上所产生的冲击干扰主要是由印制导线的电感成分造成的,因此应尽量减小印制导线的电感量。印制导线的电感量与其长度成正比,与其宽度成反比,因而短而精的导线对抑制干扰是有利的。时钟引线、行驱动器或总线驱动器的信号线常常载有大的瞬变电流,印制导线要尽可能地短。对于分立元件电路,印制导线宽度在1.5mm左右时,即可完全满足要求;对于集成电路,印制导线宽度可在0.2~1.0mm之间选择。

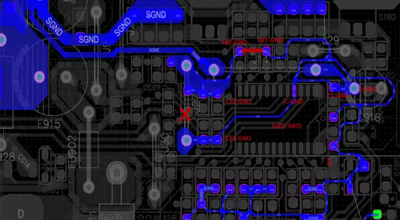

二、采用正确的布线策略

采用平等走线可以减少导线电感,但导线之间的互感和分布电容增加,如果布局允许,最好采用井字形网状布线结构,具体做法是印制电路板的一面横向布线,另一面纵向布线,然后在交叉孔处用金属化孔相连。

三、避免长距离的平等走线

解决EMI问题的办法很多,现代的EMI抑制方法包括:利用EMI抑制涂层、选用合适的EMI抑制零配件和EMI仿真设计等。本文从最基本的PCB布板出发,讨论PCB分层堆叠在控制EMI辐射中的作用和设计技巧。

电源汇流排

PCB设计完成后就万事大吉了?其实并不然,在PCB加工制作的过程中还经常会遇到各种各样的问题,比如波峰焊后的连锡。当然,并不是所有问题都是PCB设计的“锅”,但作为设计者,我们首先要保证自己的设计没有问题。

名词解释

波峰焊

元器件布局

Q:PCB设计中眼图到底有什么用?

A:眼图,是由于示波器的余辉作用,将扫描所得的每一个码元波形重叠在一起,从而形成眼图。

本文将带领大家了解PCB上的眼图是什么,眼图是怎样形成的,眼图中包含有哪些信息,如何根据眼图情况分辨信号质量。

1、眼图的定义

在学习PCB设计的过程中,有很多的知识需要大家了解和掌握,比如波峰焊,除了知道什么是波峰焊外,你还需要了解它的PCB设计原则以及布局要求。

波峰焊是让插件板的焊接面直接与高温液态锡接触达到焊接目的,其高温液态锡保持一个斜面,并由特殊装置使液态锡形成一道道类似波浪的现象,所以叫"波峰焊",其主要材料是焊锡条。

01、前言

我们电子产品往往60%以上-可靠性方面的问题都出现在电子线路板的PCB设计上;工作及性能良好的PCB需要相关的理论及实践经验;我在产品的设计实践中经常碰到各种各样的问题;比如电子线路板不能通过系统EMS的测试标准,测试关键器件IC的功能引脚时出现高频噪声的问题,电路功能IC引脚检测到干扰噪声进行异常保护等等。通过不断的理论与实践结合;用实战检验我们的理论和实践的差异点!优良的设计跟长期的经验总结是密不可分的!!

我分享一下开关电源与IC控制器PCB设计思路给电子设计爱好者参考。

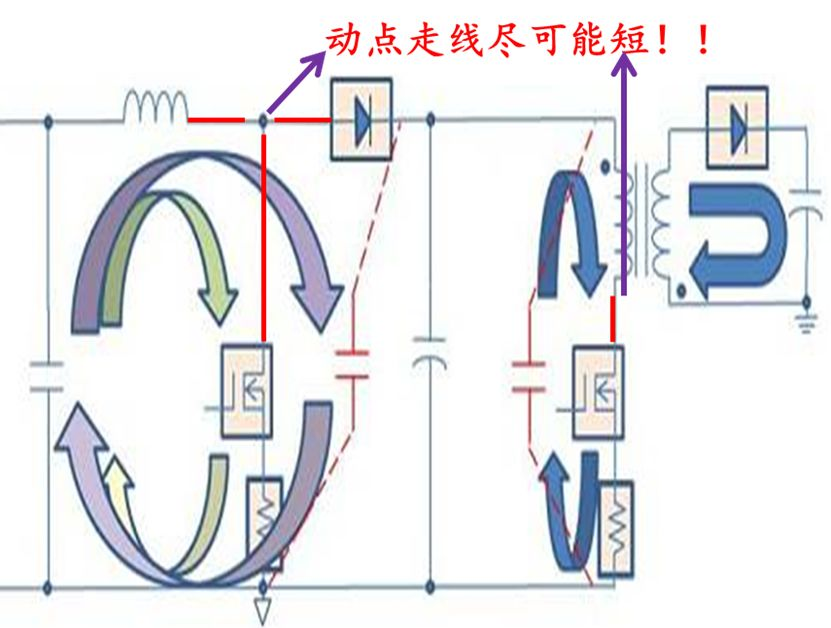

02、开关电源通过以下的原理示意图分享设计总体原则

图示为我们常用的两种开关电源的拓扑结构。

A.开关电源拓扑主电流回流路径面积最小化;驱动脉冲电流回路最小化。

B.对于隔离开关电源拓扑结构,电流回路被变压器隔离成两个或多个回路(原边和副边),电流回路要分开最小回流面积布局布线设计。

PCI-Express(peripheral component interconnect express)是一种高速串行计算机扩展总线标准,它原来的名称为“3GIO”,是由英特尔在2001年提出的,旨在替代旧的PCI,PCI-X和AGP总线标准。

PCIe属于高速串行点对点双通道高带宽传输,所连接的设备分配独享通道带宽,不共享总线带宽,主要支持主动电源管理,错误报告,端对端的可靠性传输,热插拔以及服务质量(QOS)等功能

下面是关于PCIE PCB设计的规范:

1、从金手指边缘到PCIE芯片管脚的走线长度应限制在4英寸(约100MM)以内。

2、PCIE的PERP/N,PETP/N,PECKP/N是三个差分对线,注意保护(差分对之间的距离、差分对和所有非PCIE信号的距离是20MIL,以减少有害串扰的影响和电磁干扰(EMI)的影响。芯片及PCIE信号线反面避免高频信号线,最好全GND)。

3、差分对中2条走线的长度差最多5MIL。2条走线的每一部分都要求长度匹配。差分线的线宽7MIL,差分对中2条走线的间距是7MIL。