时钟芯片常见问题解答

cathy -- 周二, 02/13/2018 - 10:40

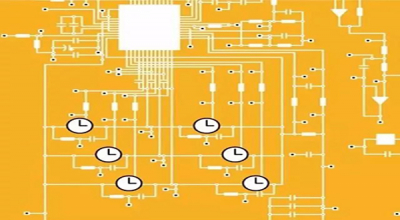

电子系统的心脏是时钟链路。时钟的原理和基础是锁相环和 DDS。时钟通过频率合成,提供所需要的频率、电平驱动、时钟同步等功能。相位噪声和抖动特性是时钟输出信号最重要和最基本的参数。锁相环的各个组成部分,包括参考源、参考分频、鉴相器、环路滤波器、压控振荡器等都对最终 PLL 的输出贡献噪声。

电子系统的心脏是时钟链路。时钟的原理和基础是锁相环和 DDS。时钟通过频率合成,提供所需要的频率、电平驱动、时钟同步等功能。相位噪声和抖动特性是时钟输出信号最重要和最基本的参数。锁相环的各个组成部分,包括参考源、参考分频、鉴相器、环路滤波器、压控振荡器等都对最终 PLL 的输出贡献噪声。

差分信号

差分传输是一种信号传输的技术,区别于传统的一根信号线一根地线的做法,差分传输在这两根线上都传输信号,这两个信号的振幅相等,相位相反。在这两根线上传输的信号就是差分信号。差分信号又称差模信号,是相对共模信号而言的。

贸泽电子 Steven Keeping

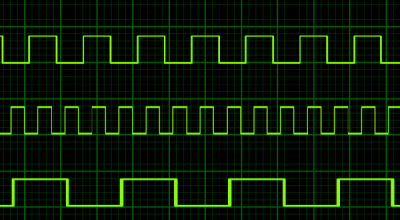

本期我将讨论在测量较低时钟频率的相位噪声和相位抖动时出现的一个非常常见的问题。在所有条件相同的情况下,我们通常期望分频的低频时钟产生比高频时钟更低的相位噪声。在数量上,你可能会记得这是20log(N)规则。

导读:本文针对用单片机制作电子钟或要求根据时钟启控的控制系统时,出现的校准了的电子时钟的时间竟然变快或是变慢了的情况而提出的一种解决方案。

单片机应用中,常常会遇到这种情况,在用单片机制作电子钟或要求根据时钟启控的控制系统时,会突然发现当初校准了的电子时钟的时间竟然变快或是变慢了。