射频板叠层结构及布线要求,你掌握了吗?

cathy -- 周五, 02/26/2021 - 11:01

1、射频板叠层结构

RF PCB单板的叠层结构除了要考虑射频信号线的阻抗以外,还需要考虑散热、电流、器件、EMC、结构和趋肤效应等问题,通常我们在多层印制板分层及堆叠中遵徇以下一些基本原则:

1、射频板叠层结构

RF PCB单板的叠层结构除了要考虑射频信号线的阻抗以外,还需要考虑散热、电流、器件、EMC、结构和趋肤效应等问题,通常我们在多层印制板分层及堆叠中遵徇以下一些基本原则:

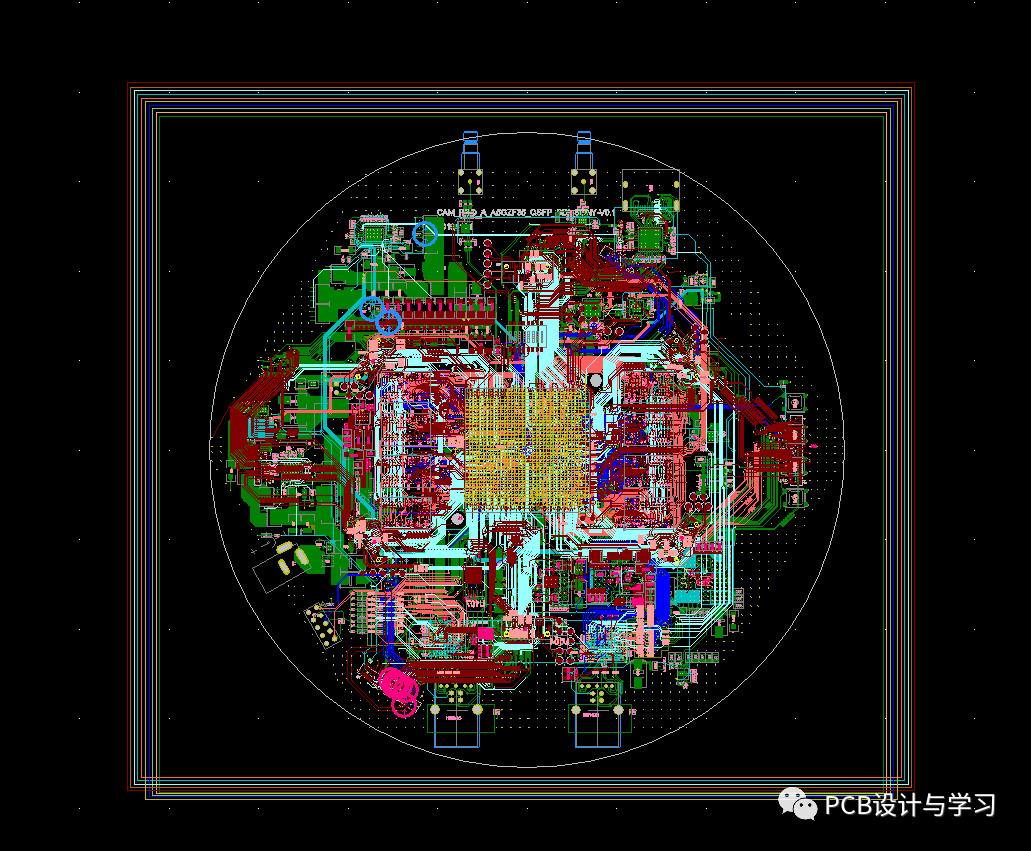

10层PCB所有层总览。

进行铺铜后的所有层总体效果。

总的来说叠层设计主要要遵从两个规矩:

1.每个走线层都必须有一个邻近的参考层(电源或地层)。

2.邻近的主电源层和地层要保持最小间距,以提供较大的耦合电容。

下面列出从两层板到八层板的叠层来进行示例讲解:

一、单面PCB板和双面PCB板的叠层

对于两层板来说,由于板层数量少,已经不存在叠层的问题。控制EMI辐射主要从布线和布局来考虑;

单层板和双层板的电磁兼容问题越来越突出。造成这种现象的主要原因就是因信号回路面积过大,不仅产生了较强的电磁辐射,而且使电路对外界干扰敏感。要改善线路的电磁兼容性,最简单的方法是减小关键信号的回路面积。

关键信号:从电磁兼容的角度考虑,关键信号主要指产生较强辐射的信号和对外界敏感的信号。能够产生较强辐射的信号一般是周期性信号,如时钟或地址的低位信号。对干扰敏感的信号是指那些电平较低的模拟信号。

单、双层板通常使用在低于10KHz的低频模拟设计中:

确定最佳印刷电路板布局的关键之一是了解信号返回电流的实际流动方式和方向,大多数设计人员只考虑信号电流的流向(显然是在信号迹线上),而忽略了返回电流所经过的路径。

为了解决上述问题,我们必须了解高频电流是如何在导体中流动的。

首先,最低阻抗的返回路径是在信号迹线正下方的平面上(不管这是电源还是地平面),因为这提供了最低的电感路径,这也产生了最小的电流环路面积可能。

其次,由于“集肤效应”,高频电流不能穿透导体,因此高频时导体中的所有电流都是表面电流。

这种影响将发生在所有频率超过30MHz的1盎司铜层,因此,PCB中的平面实际上是两个导体而不是一个导体。

在平面的上表面会有电流,在平面的下表面会有不同的电流或者根本没有电流。

当现有返回路径出现不连续时,就会出现严重的EMC问题。这些不连续性导致回流电流在更大的回路中流动,从而增加了电路板的辐射,增加了相邻线路之间的串扰,造成波形失真。

此外,在恒阻抗pcb板中,返回路径的不连续性会改变线路的特性阻抗。

下面讨论最常见的返回路径不连续。

在高速PCB设计流程里,叠层设计和阻抗计算是登顶的第一梯。阻抗计算方法很成熟,不同软件的计算差别不大,相对而言比较繁琐,阻抗计算和工艺制程之间的一些"权衡的艺术",主要是为了达到我们阻抗管控目的的同时,也能保证工艺加工的方便,以及尽量降低加工成本。

计流