在PCB设计中高效地使用BGA信号布线技术

cathy -- 周三, 01/24/2018 - 16:13

球栅阵列(BGA)封装是目前FPGA和微处理器等各种高度先进和复杂的半导体器件采用的标准封装类型。用于嵌入式设计的BGA封装技术在跟随芯片制造商的技术发展而不断进步,这类封装一般分成标准和微型BGA两种。这两种类型封装都要应对数量越来越多的I/O挑战,这意味着信号迂回布线(Escaperouting)越来越困难,即使对于经验丰富的PCB和嵌入式设计师来说也极具挑战性。

球栅阵列(BGA)封装是目前FPGA和微处理器等各种高度先进和复杂的半导体器件采用的标准封装类型。用于嵌入式设计的BGA封装技术在跟随芯片制造商的技术发展而不断进步,这类封装一般分成标准和微型BGA两种。这两种类型封装都要应对数量越来越多的I/O挑战,这意味着信号迂回布线(Escaperouting)越来越困难,即使对于经验丰富的PCB和嵌入式设计师来说也极具挑战性。

对于新手来说,在单片机的电路设计中可能不会很注意电路设计中电磁干扰对设计本身的输入输出的影响,但是对于一个电子工程师来说其中的厉害关系就不言而喻了,它不仅关系了单片机在控制在中的能力和准确度,还关系到企业在行业中的竞争。

对电磁干扰的设计我们主要从硬件和软件方面进行设计处理,下面就是从单片机的PCB设计到软件处理方面来介绍对电磁兼容性的处理。

初次接触高速讯号或DDR设计的人,可以找到一些在谈走线绕等长的 旧资料(当中不乏过去大厂的design guide),但近几年一些DDRII(或更快)的design rule,渐渐改以定义setup time, hold time budget with jitter取代length-matching routing rule,并且改以强调对时序图的理解与使用模拟(margin predic

1. 引言

我们常把晶振比喻为数字电路的心脏,这是因为,数字电路的所有工作都离不开时钟信号,晶振直接控制着整个系统,若晶振不运作那么整个系统也就瘫痪了,所以晶振是决定了数字电路开始工作的先决条件。

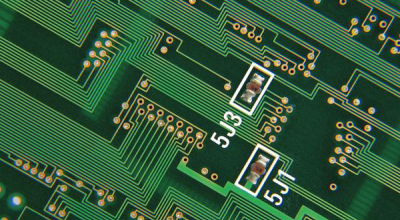

[导读]电路板尺寸和布线层数需要在设计初期确定。如果设计要求使用高密度球栅数组(BGA)组件,就必须考虑这些器件布线所需要的最少布线层数。布线层的数量以及层叠(stack-up)方式会直接影响到印制线的布线和阻抗。

高频电路往往集成度较高,布线密度大,采用多层板既是布线所必须,也是降低干扰的有效手段。在PCB Layout阶段,合理的选择一定层数的印制板尺寸,能充分利用中间层来设置屏蔽,更好地实现就近接地,并有效地降低寄生电感和缩短信号的传输长度,同时还能大幅度地降低信号的交叉干扰等,所有这些方法都对高频电路的可靠性有利。

印刷电路板 (PCB) 是电子产品的躯体,最终产品的性能、寿命和可靠性依赖于其所构成的电气系统。如果设计得当,具有高质量电路的产品将具有较低的现场故障率和现场退货率。因此,产品的生产成本将更低,利润更高。为了按时生产高质量的 PCB 板,同时不增加设计时间且不产生代价高昂的返工,必须尽早在设计流程中发现设计和电路完整性问题。

一、影响EMC的因数

由于体积和尺寸都很小,对日益增长的可穿戴物联网市场来说几乎没有现成的印刷电路板标准。在这些标准面世之前,我们不得不依靠在板级开发中所学的知识和制造经验,并思考如何将它们应用于独特的新兴挑战。有三个领域需要我们特别加以关注,它们是:电路板表面材料,射频/微波设计和射频传输线。