资料下载:PLL应用的常见问题及解决方法

cathy -- 周五, 08/14/2020 - 09:21

锁相环(PLL)是一种反馈系统,其中电压控制振荡器(VCO)和相位比较器相互连接,使得振荡器可以相对于参考信号维持恒定的相位角度。在使用PLL的过程中您都遇到过哪些问题呢?

锁相环(PLL)是一种反馈系统,其中电压控制振荡器(VCO)和相位比较器相互连接,使得振荡器可以相对于参考信号维持恒定的相位角度。在使用PLL的过程中您都遇到过哪些问题呢?

Peter Delos ADI公司

摘要

对于数字波束成形相控阵,要生成LO,通常会考虑的实现方法是向分布于天线阵列中的一系列锁相环分配常用基准频率。对于这些分布式锁相环,目前文献中还没有充分记录用于评估组合相位噪声性能的方法。

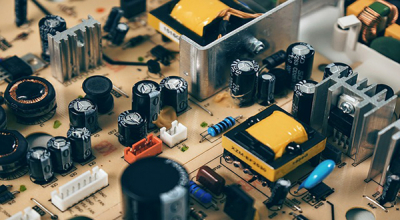

锁相环(PLL)电路存在于各种高频应用中,从简单的时钟净化电路到用于高性能无线电通信链路的本振(LO),以及矢量网络分析仪(VNA)中的超快开关频率合成器。

今天,我们就参考上述各种应用来介绍PLL电路的一些构建模块,以指导器件选择和每种不同应用内部的权衡考虑,这对新手和PLL专家均有帮助。

几乎每个RF和微波系统都需要频率合成器。频率合成器产生本振信号以驱动混频器、调制器、解调器及其他许多RF和微波器件。频率合成器常被视为系统的心跳,创建方法之一是使用锁相环(PLL)频率合成器。

锁相环(PLL)是现代通信系统的基本构建模块PLLs 通常用在无线电接收机或发射机中,主要提供"本振"(LO)功能;也可用于时钟信号分配和降噪,而且越来越多地用作高采样速率模数或数模转换的时钟源。

由于每一代PLL的噪声性能都在改善,因此电源噪声的影响变得越来越明显,某些情况下甚至可限制噪声性能。我们今天讨论下图1所示的基本PLL方案,并考察每个构建模块的电源管理要求。