深度丨采用分布式PLL系统评估相位噪声的方法

cathy -- 周一, 04/15/2019 - 09:41

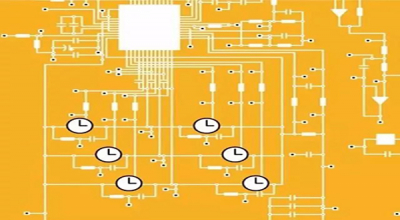

对于数字波束成形相控阵,要生成本地振荡器(LO) ,通常会考虑的实现方法是向分布于天线阵列中的一系列锁相环分配常用基准频率。对于这些分布式锁相环,目前文献中还没有充分记录用于评估组合相位噪声性能的方法。

对于数字波束成形相控阵,要生成本地振荡器(LO) ,通常会考虑的实现方法是向分布于天线阵列中的一系列锁相环分配常用基准频率。对于这些分布式锁相环,目前文献中还没有充分记录用于评估组合相位噪声性能的方法。

Peter Delos ADI公司

摘要

对于数字波束成形相控阵,要生成LO,通常会考虑的实现方法是向分布于天线阵列中的一系列锁相环分配常用基准频率。对于这些分布式锁相环,目前文献中还没有充分记录用于评估组合相位噪声性能的方法。

相位噪声的含义

本期我将讨论在测量较低时钟频率的相位噪声和相位抖动时出现的一个非常常见的问题。在所有条件相同的情况下,我们通常期望分频的低频时钟产生比高频时钟更低的相位噪声。在数量上,你可能会记得这是20log(N)规则。

随着电子技术的发展,器件的噪声系数越来越低,放大器的动态范围也越来越大,增益也大有提高,使得电路系统的灵敏度和选择性以及线性度等主要技术指标都得到较好的解决。同时,随着技术的不断提高,对电路系统又提出了更高的要求,这就要求电路系统必须具有较低的相位噪声,在现代技术中,相位噪声已成为限制电路系统的主要因素。低相位噪声对于提高电路系统性能起到重要作用。