高级硬件工程师设计电路,最想解决哪几个问题?

cathy -- 周四, 03/04/2021 - 13:27

电磁兼容是指设备或系统在其电磁环境中能正常工作且不对该环境中任何事物构成不能承受的电磁骚扰的能力。

电路设计是创建电子电路的过程,旨在实现特定的功能或任务。电路可以是数字电路、模拟电路、混合信号电路或射频电路,根据应用的不同。

电磁兼容是指设备或系统在其电磁环境中能正常工作且不对该环境中任何事物构成不能承受的电磁骚扰的能力。

电路设计不仅有很多技巧,同样也存在很多误区。本文将介绍电路稳定性设计当中的十个误区。

误区1:产品故障=产品不可靠

这几天在网络上看到一个非常不错的电路,这里通过电流走向,详细跟大家分析一下这个电路的精髓。

如果现在给大家出一个题目,要求用最低成本,稳定可靠的实现一个按键开关电路,也就是按一下按键,IO口输出1,再按一下,IO口输出0,并且电平要保持状态。

1、单片机上拉电阻的选择

当我们的电路既可以由外部USB电源供电,也可以由锂电池供电时,我们需要进行如下的逻辑设置:

1、外部电源供电时,断掉锂电池的供电;

2、断开外部供电时,由锂电池供电。

下面是作者在设计电路时所使用的电路:

双电压整流电路需要搭载两个桥式电路吗?

单片射频器件大大方便了一定范围内无线通信领域的应用,采用合适的微控制器和天线并结合此收发器件即可构成完整的无线通信链路。它们可以集成在一块很小的电路板上,应用于无线数字音频、数字视频数据传输系统,无线遥控和遥测系统,无线数据采集系统,无线网络以及无线安全防范系统等众多领域。

1、数字电路与模拟电路的潜在矛盾

向用户指示系统故障相当重要,尤其是在汽车照明方面。

以汽车尾灯中的转向指示灯为例,它表示驾驶员想要变换车道或转向。LED是用于转向指示灯的一种常见且不断增强的光源,由一个双级LED驱动电路拓扑驱动。该双极LED驱动电路拓扑由一个第一级降压稳压器和一个第二级恒流线性LED驱动器构成,具有热效率优势。

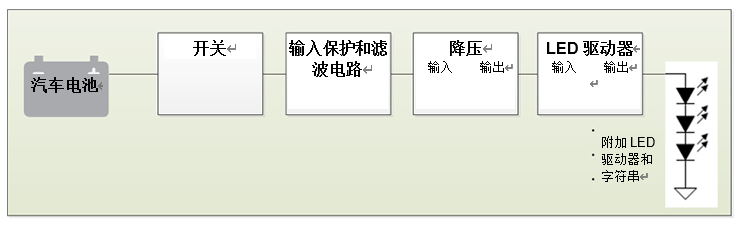

图1中基于LED的转向指示灯模块包括一个典型汽车电池、开关、输入滤波器、降压稳压器和几个LED驱动器。当车灯停止正常运行时,驾驶员将如何得知?如何确定是系统的哪个部分出现故障?

降压稳压器和LED驱动器集成电路实施诊断功能,以便检测故障事件。例如,“电源正常”信号是一种诊断特征,用于指示降压的输出是否处于调节状态。同样,恒流LED驱动器输出故障信号来指示LED短路和开路。

在本文中,我将着重讨论汽车尾灯故障电路,以及如何结合降压稳压器的PWRGD信号和LED驱动器的故障信号来设计故障电路。

电路设计并不是想当然,你脑子一拍就可以设计出来,有没有经验设计出来的东西是相差千里。今天我们来看看电子工程师会出现的下面的几个误区,你是不是也这样想的。

误区一:这板子的PCB 设计要求不高,就用细一点的线,自动布吧。

电路基础

电压电流

● 电流的参考方向可以任意指定,分析时:若参考方向与实际方向一致,则i>0,反之i<0。