1、射频电路的布局和连接尽可能地短

由于传输线拐角处的阻抗突变会造成信号反射,高频信号将作为电磁场能量辐射到空间中。结果,经“拐角”之后的信号电平值可能下降。 因此,在设计高频电路时,必须精心设计RF布局以使得RF走线拐角角度尽可能的小。

设计RF电路时,如果板上有足够的空间,则将RF相关元器件布置成尽可能直线化。 通过直线化布局布线布线,可以避免信号反射,防止信号电平值降低,以满足设计指标。

设计要点:在低频电路的时,信号走线成直角也可以正常工作。 然而,在高频电路中,即使走线铜箔宽度的细微变化也会产生影响,因为走线宽度变化,特征阻抗就会受到影响,发生信号反射,降低信号电平值,达不到设计指标。

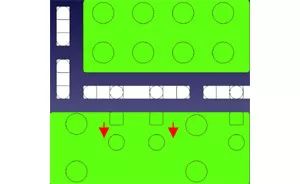

2、在RF走线的拐角处通过放置元件或者圆弧走线的方式来降低特性阻抗突变造成的影响。

还是围绕老wu第一点说的【避免特征阻抗突变】的原则,如果板上空间富裕,优先通过布局实现RF走线的短和直,如果布局空间不允许,需要拐角走线,一定避免直角或45°拐角走线,要走圆弧走线,如果实在要走直角了,可以通过放置元件通过元件的摆位的方式来替代走线来做90°角的转折,这样可以最大化避免阻抗突变造成的信号反射影响。

设计要点:在高频电路的情况下,重要的是改善RF线路的布局,即遵循【避免特征阻抗突变】的原则

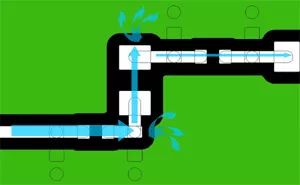

3、为接地焊盘单独接地,避免共用接地过孔

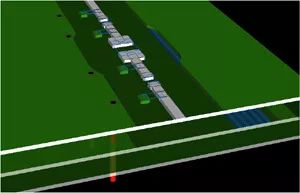

设计高频电路时,必须认真处理RF信号走线和GND之间的连接。 在上图的反例中,RF元件的接地焊盘共用一个接地过孔与GND平面连接。

下图的改进实例中,为每个接地焊盘就近打了接地过孔与GND平面连接,接地环路更小,将噪声降至最低。

设计要点:与常规电路相比,高频电路对于与GND的连接必须严格处理,为每个接地焊盘单独提供一个接地过孔以最短的途径与地平面进行连接。

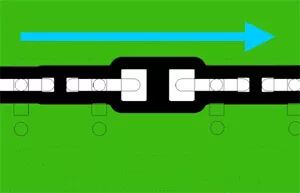

4、射频巴伦差分走线要保持对称

设计高频电路时,必须注意同一电路部分的接线。 比如上面的反例图示是射频巴伦(balun)电路,左右走线不对称。

下图改进的巴伦电路,缩短射频信号走线长度并且左右对称。

设计要点: 在高频电路的情况下,布线的影响很大。

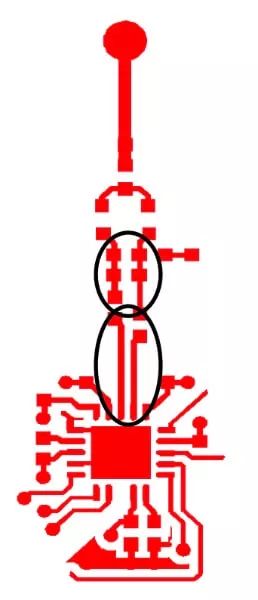

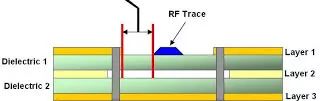

5、RF信号走线50欧阻抗隔层参考尽量扩大挖空区域

对于具有RF/高速信号混合的PCB、RF射频信号走线需要控50欧阻抗,高速传输线也需要控阻抗,比如常见的单独50欧差分100欧,高速传输线为了有更多的空间走线,尽量走小的线宽,比如BGA区域4mil线宽/线距,但射频信号为了避免插入损耗(Insertion Loss),插入损耗主要包括介质损耗、导体损耗、辐射损耗和泄露损耗几个部分,是各种损耗成分的总和。射频信号适当加大走线线宽可以降低插入损耗,但线宽也不是越大越好,对于微波及毫米波的电路应用,较宽的线宽容易产生不必要的杂散信号,影响信号的传输。

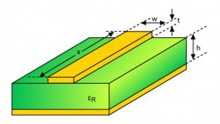

一般RF走线线宽20mil,以对应0402的焊盘,但要满足50欧的阻抗,宽的线宽就意味着走线与参考层的距离要拉大(影响阻抗的因素包括介质厚度、介电常数、线宽、铜厚、阻焊油墨厚度,但其中介质厚度和线宽的影响最为显著,一般控阻抗要么调线宽要么控介质厚度)。

高速传输线线宽4mil、射频走线需要20mil,如果都是参考同一个平面,介质厚度是固定的,那就满足不了不同线宽控到同一阻抗。鉴于高速传输线需要控阻抗的走线较多,所以就拿射频走线来做调整,拉大介质厚度的方法就是隔层参考控阻抗,比如走线在顶层,把第二层挖空,参考第三层的平面,达到比较厚的介质厚度。

但是这个挖空也是有讲究的,老wu看到有的同学直接复制顶层的射频走线到第二层作为参考层的挖空区域,但…这个挖空区域还不够宽,要避免第二层的铜箔对阻抗造成影响,第二层的挖空区域要尽量大,至少也要3倍的射频走线的线宽。

高频PCB设计概要之一

高频PCB设计概要之一 相关阅读:

高频PCB设计概要之一

转载自 吴川斌的博客 https://www.mr-wu.cn

本文链接地址: 高频PCB设计概要之二 https://www.mr-wu.cn/gao-pin-pcb-she-ji-gao-yao-zhi-er/

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理(联系邮箱:cathy@eetrend.com)。