随着射频元器件和子系统以及高密度数字信号处理电子器件的快速发展,多输入多输出(MIMO)技术正引起广泛关注,因为该技术可通过多路复用来提高数据速率,或通过空间分集使系统性能至少提高一个数量级。鉴于相控阵雷达、波束赋形和测向系统等各种电子战和雷达应用正在广泛采用MIMO系统,而应用此类MIMO系统必须克服与信道间相位和幅度同步等相关的关键技术难题,才能一致地接收和处理每个输入/输出采集或生成的数据。因此,德州奥斯汀NI总部的两位技术大神Shivansh Chaudhary以及Eddie Rodriguez试图通过本文告诉你应对多通道相位相干系统测试挑战应该往哪些方向使劲

他们认为,每个通道的精确相位和振幅同步对多通道相位相干系统的测试和验证提出了严峻的挑战。为了高效地测试这些系统,测试和测量设备必须提供同等或更高的信号相干精度,并能够对相位、时间、频率和幅度进行完全控制。

本文三大主旨

-

本文将概述测试多通道相位相干测量和生成系统的挑战和要求,并介绍这些要求如何体现在测试仪器设计规范中。

-

另外,本文还将介绍使用商用软件定义的模块化仪器来开发多通道相位相干测试系统的操作步骤,以及实时校准的详细过程,以实现相位和幅度的精细对准。

-

最后,本文介绍了一个下一代多通道相位相干测试系统示例,包括验证系统是否满足要求的测试。

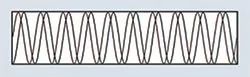

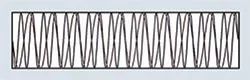

相位一致性这一属性适用于两个或更多数量的信号,是指在肉眼可辩的时间内信号之间的相对相位保持恒定。图1显示了具有相同频率的两个通道的相位一致性概念图。图2显示了两个不同频率的通道的相位一致性,其中信号在每N个周期内具有指定的相位关系。在实现相位相干之后,可以使用相位对准方法来补偿相干信号之间的恒定相位差。

在实际的MIMO测试系统中,无线电硬件应能够跨多个通道采集和生成相位相干和相位对准的信号。许多现代电子战系统利用多通道相位相干系统执行无源雷达系统的测向等任务,或在抗干扰通信中提供多径冗余。例如,相控阵雷达使用数百个相位相干的发射/接收(Tx / Rx)模块来实现快速电子束转向,通过改变馈送组件的相应信号的相对相位,使有效辐射图的阵列在期望的方向上被增强,在不期望的方向上被抑制。

合成孔径干涉雷达(InSAR)等地理定位系统采用若干相位相干接收机,通过精确地定位发射或反射信号的位置来检测地震和洪水等事件的位置。除了设计的复杂性增加外,多通道相位相干系统中紧密同步和精细对准也是国防与航空航天行业的严苛测试要求之一。

构建多通道相位相干系统的测试系统的主要难题是相干信号的相位对准。此外,系统需要能够在相当长的时间内维持相位一致性和对准。然而,由于温度、热膨胀、电缆长度不匹配、不相关相位噪声、ADC采样时钟、相位噪声和量化噪声等的影响,相位会发生漂移。在微波频率下,电缆长度、放大器和滤波器之间的细微差异甚至也会导延迟或相移,从而破坏原有的关系。

对于多信道设计工程师来说,组件的相位稳定性、非线性AM/PM效应和群延迟变化都会引起相位失配。测向和波束赋形相关的许多应用要求通道之间的相位关系保持恒定,相位漂移不超过1°。

测试多通道相位相干系统

以下部分将讨论使用模块化软件设计的仪器方法来应对多通道相位相干系统测试系统开发挑战的技术。多通道系统面临的第一个挑战是通过创建一致且可靠的触发机制来确保所有通道同时开始采集或生成数据。通常,通道之间的对准要求时间差小于1ns,而在实际应用中,布线往往成为实现这一目标的障碍。测试系统中的长电缆使得触发时间需要加上较长的传播时间,每米同轴电缆的传播时间约5ns,因而需要简化触发器分配。

鉴于由偏移和抖动引起的延迟和时序不确定性,分配必要的时钟和触发来实现多设备同步并非易事。而基于PXI的模块化仪器平台就非常适合用来应对这些复杂性。PXI架构允许设计人员利用PXI的独特功能来实现高级多设备同步,例如触发总线、星型触发器和公共系统参考时钟。

一种同步方法是NI-TClk,该技术使用另一个时钟域来实现采样时钟的对准以及触发器的分配和接收3。多通道相位相干测试系统的设计人员可以使用这种方法将一开始没对准但锁相至公共参考时钟的采样时钟进行对准,并且能够实现各个设备的准确同步触发。

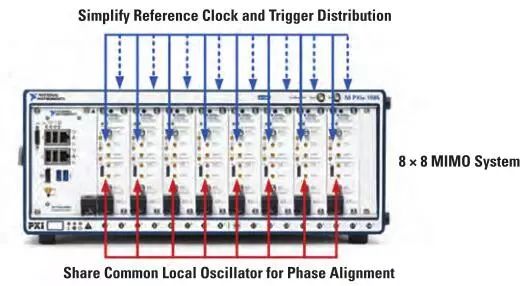

图3显示了基于八个矢量信号收发器(VST)的8 x 8 MIMO配置,每个VST能够在单个18槽机箱中生成和采集1 GHz瞬时RF带宽信号,并使用NI TClk和一个共享的PXI参考时钟实现偏斜低于500 ps的紧密同步。

实现相位的一致和对准

大多数传统射频仪器、分析仪或发生器都允许共享参考时钟(通常为10 MHz),有时会共享起始触发。虽然共享这些时钟信号足以保证同步的信号采集和生成,但无法保证相位一致。例如,两个矢量信号分析仪之间只共享10 MHz参考时钟的情况。

在这种情况下,两个分析仪将从公共的10 MHz时钟独立地导出其本地振荡器。在短时间内,信号可能看起来具有恒定的相位差,但随着时间的推移,每个通道的相位将会发生漂移。这是因为每个LO独立于10 MHz参考时钟导出,而且在合成每个LO时引入的锁相环(PLL)噪声对于每个通道都是独立的。因此,仅共享10MHz参考时钟的多通道RF系统将会出现明显的通道间相位偏斜。

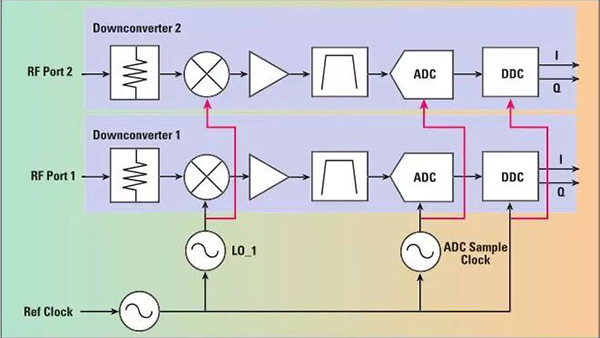

实现相位相干和对准的更好方法是从单个PLL导出所有通道共享的单个LO,如图4所示。当直接共享LO时,每个下变频器具有相同的相位噪声4。

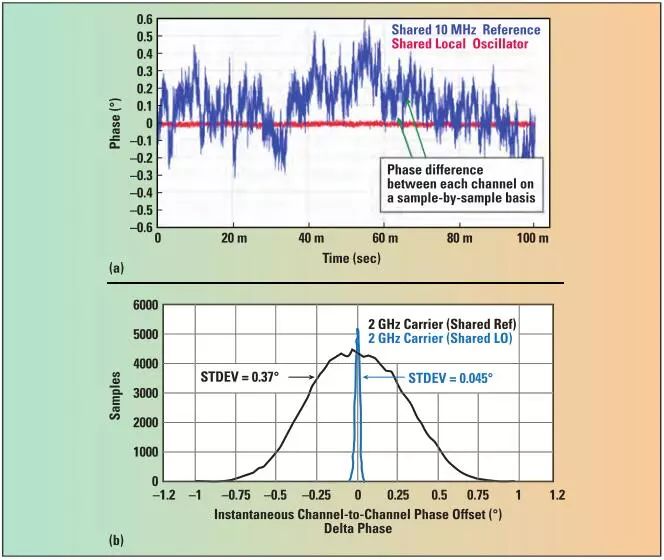

请观察图5a中使用两种不同的同步方法时的通道间偏斜。蓝色线表示的是当每个分析仪仅共享10 MHz参考时钟而不共享LO时的相位差。红色线表示每个下变频器信号链之间直接共享本地振荡器时每个通道之间的相位差。从图中可以看出,直接共享LO要比仅共享10 MHz参考时钟表现出明显更紧密的相位对准。

测量直接共享LO的好处的另一种方法是查看通道间相位误差的直方图,如图5b所示。对于仅共享10 MHz参考时钟的情况,可以看到相位变化的范围明显较宽(六西格玛置信度水平大于1°)。而在直接共享LO的情况下,置信度水平在0.2°以内。

实时在线处理

实时处理对于测试电子战系统的许多方面都很重要。对于涉及波束赋形或测向的测试应用,如无源雷达,由于信道特性变化迅速,实时计算信道矩阵是很重要的。由主机处理器处理RF采样信号不仅速度非常慢,而且还会消耗数据处理能力和总线带宽。相反,我们可以将采样信号转移到板载FPGA,或通过高带宽PXI总线传输到额外的FPGA协处理器上进行在线信号处理。

对于许多测试应用,存储和播放信号同样非常重要。存储波形可帮助我们深入观察多通道数据,并能够捕获较短时间或较低频率的杂散信号。对于监测未经授权的信号或零星干扰,存储的信号可作为特定地理区域的RF活动的证据。真实信号的采集也可用于验证未来的通信系统是否能够适应真实的场景。

PCI Express架构通过支持多个设备之间的点对点传输来实现这些要求,从而可以实时持续地传输和处理数据,或者长时间存储到磁盘并进行后期处理。这种系统使得研究人员和开发人员能够从多通道射频源采集和存储信息,以进行仔细观察或离线处理。之后,在实验室中,数据可以作为激励信号进行操作和回放,以验证算法、信道模型、硬件配置和真实系统的其他方面。

无论在实验室还是部署在现场,尺寸、重量和功率(SWaP)都是电子战应用中测量设备的重要考量因素。随着先进电子战系统的复杂性和计算能力不断增加,设计工程师正在利用PXI平台的先进技术和模块化特性来构建多功能系统,以满足SWaP需求。

多通道相位相关测试系统

下面将介绍一个可以解决多通道相位相干射频系统测试和验证难题和要求的测试系统。该测试系统建立在基于平台的模块化硬件和软件定义的仪器的基础上。

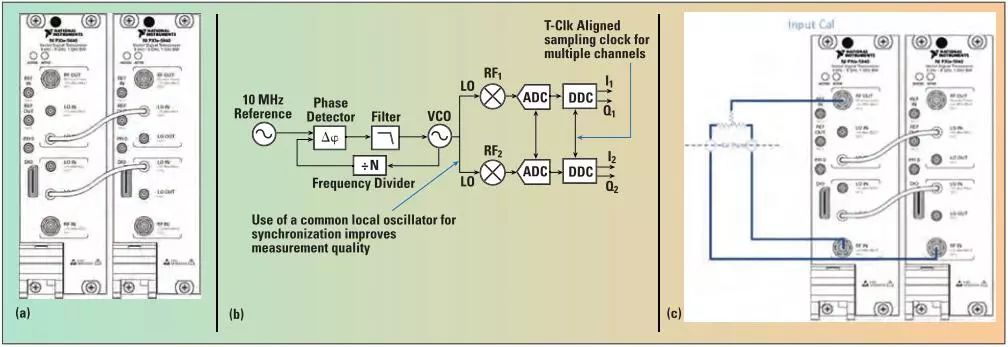

图6a显示了一个NI双通道相位相干测试系统配置,该系统基于PXIe-1085机箱,这是一款18槽机箱,内置10 MHz参考时钟、PXI触发总线和PXI模块的星型触发器。对于RF仪器,PXIe-5840 VST用于构成2 x 2 MIMO配置。

以下是开发多通道相位相干测试系统的步骤:

-

步骤1:第一步是配置两个VST,通过软件共享PXIe-1085机箱的通用PXI参考时钟,并在发生器和分析仪之间物理共享LO,如图6b所示。 VST原生支持NI-TClk技术,确保了所有通道同时开始采集/生成,并可实现小于500 ps通道间偏斜。我们通过系统校准将通道间偏斜进一步降低了一个数量级,达到低于50ps。

-

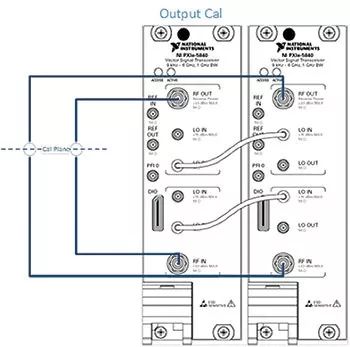

步骤2: VST同步后,下一步是确保相位和幅度一致。在本例中,首先分析仪之间存在多通道相位一致性。在这一步骤中,其中一个VST作为连续波信号的源,该连续波信号将作为校准信号。接着这个VST生成的信号通过双向分路器分离,并馈送到两个VST的RF输入端口,如图6c所示。

-

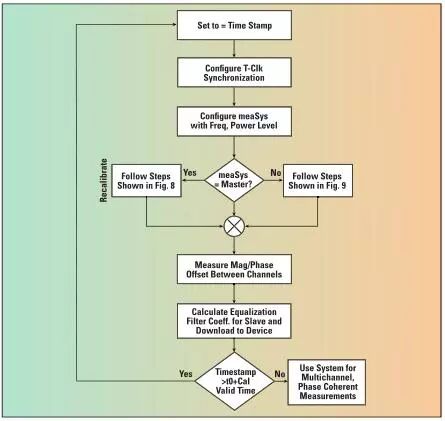

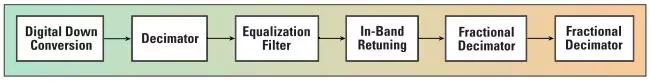

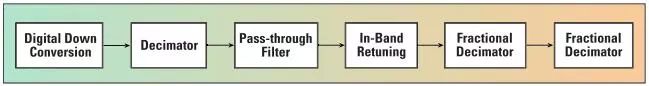

步骤3:接下来是应用基于FPGA的实时校准过程,以在两个VST之间进行相位和幅度精细对准5。该校准过程使用基于LabVIEW FPGA的VST的板载XilinxVirtex 7 FPGA来实现。图7、8和9描述了校准过程中涉及到的步骤。该算法可从双信道扩展到八信道。MeasSys表示多通道相位相干采集系统,Timestamp表示测量的初始时间实例,freq表示连续波频率,cal Validtime表示系统需要重新校准的间隔时间。

-

步骤4: 现在系统已经可以进行多通道相位相干测量,下一步是配置多通道相位相干生成系统。图10显示了此步骤的硬件配置,其中两个VST简单地以环回模式连接,具有共享LO和公共参考时钟。

-

步骤5:下一步是应用实时校准过程,对发生器之间的相位和幅度差进行微调。重复步骤3描述的过程,以实现多通道相位相干生成系统。

-

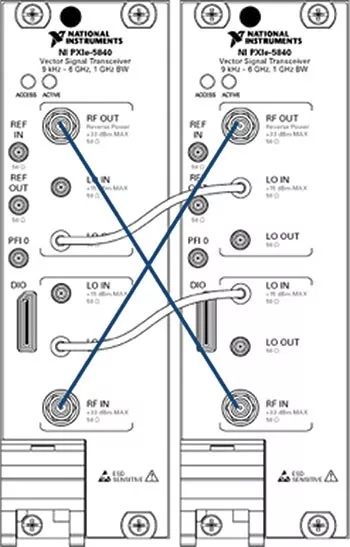

步骤6:现在,用于测试多通道相位相干射频系统的新一代系统就准备好了。这可以通过以十字交叉的方法连接两个VST来简单地进行验证,如图11所示,然后观察相位和振幅差随时间的稳定性。

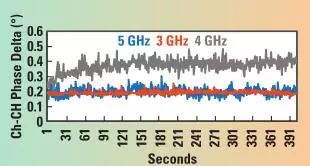

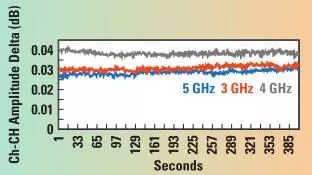

多通道相位相干测试系统需要在温度可调节的测试舱中进行测试。在应用校准算法之后,计算两个通道之间相位和幅度差,并且在3、4和5GHz频率下进行测量,如图10和11所示。注意,图12和13显示的是两个信道之间的平均相位和幅度差。

结果表明,按照上述步骤构建的下一代多通道相干测试系统实现了变化范围在±1°以内的相位差,且幅度差的变化保持在0.05 dB内。

结 论

随着多通道相位相干系统在电子战和雷达应用中的普及,对此类系统进行高效测试和部署的需求正日益凸显。此外,对于多通道RF系统,测试和测量设备能够提供同等或更高的相位和幅度对准精度是至关重要的。

本文介绍了测试多通道相位相干系统的挑战和要求,提出了一个基于平台化方法的下一代测试系统来解决这些挑战,并概述了一种基于FPGA的软件定义校准过程,通过内部校准机制来实现持续的相位一致性。

测试结果展现了多通道相位相干测试系统的相位和幅度变化的稳定性。利用PXI平台的可扩展性和模块化特性,上述双通道相位相干VST系统的架构可以进一步扩展来实现相位和幅度变化精度保持一致的4 x 4或8 x 8相位相干测试系统。

本文转载自: 恩艾NI知道

转载地址:http://mp.weixin.qq.com/s/ImjhK1uIi6ieFP3HM1bulg

声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有,如涉及侵权,请联系小编进行处理。