嵌入式应用的众口难调与IoT应用的高速发展,正在成为推动异构集成的原动力。异构集成,简单地说就是在一颗MCU芯片中“包”入不同的功能电路和模块,让MCU用各具特色的“馅料”去迎合不同应用场景中用户的口味。

通用CPU的通用性决定了它不能做到“面面俱到”,因此,加入专用的协处理器或可编程硬件加速引擎,顺理成章就成为取长补短的首选。比如高端的音频DSP、专用的安全处理单元,对于需要安全连接的智能语音识别和音频设计非常有好处。而图形图像专用硬件的集成,则打开了MCU平台进入高级HMI和视觉应用的大门。

近年来,随着IoT与万物互联的爆发,需要无线和高频相关的硬件设计,以及多种传感器的使用。在MCU中集成无线模块、传感器融合算法加速引擎等,可以满足IoT节点和穿戴设备的需要。

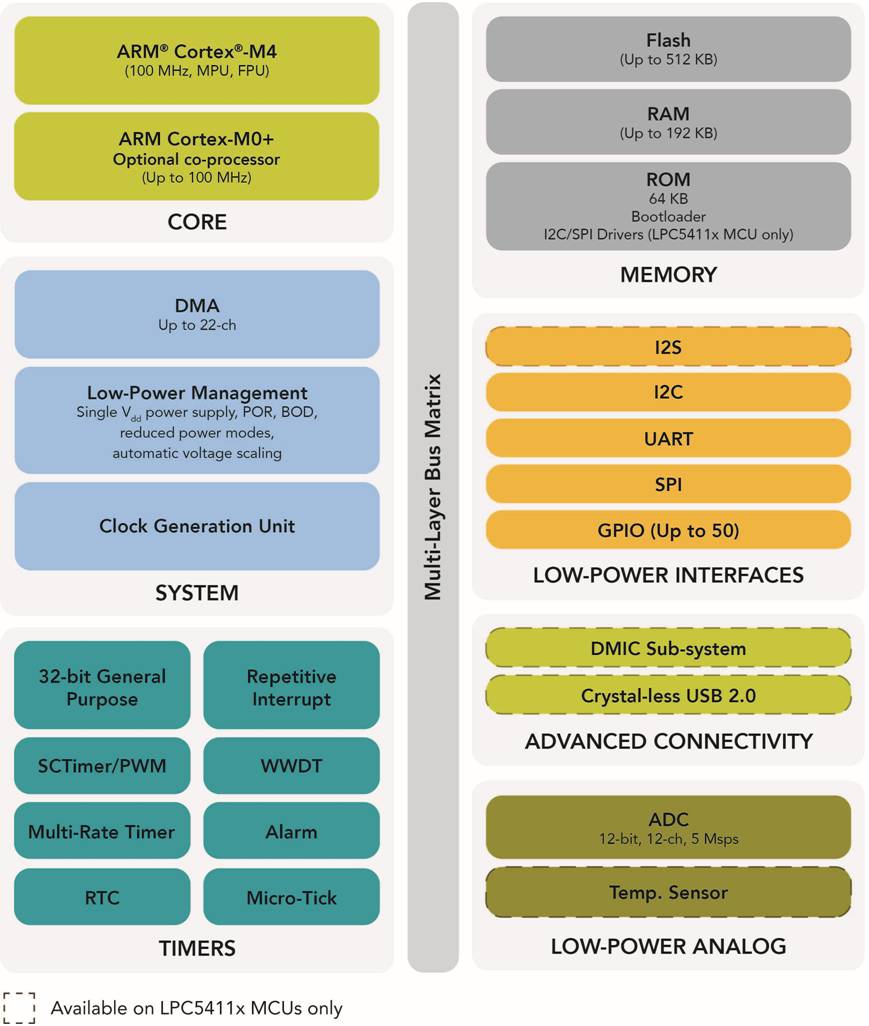

说起异构集成就要提异构多核,这类集成留给用户发挥的空间最大。比如ARM Cortex-M4与Cortex-M0+的集成,M0+可以做任务分担、负载均衡、硬件加速、组件隔离等多种应用场景,提高了能效和性能。ARM Cortex-A7 + Cortex-M4的异构,则更多是发挥M核在能效和实时性的优势。

恩智浦在异构集成领域拥有全方位的产品和解决方案。比如双核的LPC4300与LPC54100系列通用MCU;集成了ZigBee、BLE和传感器算法加速的多款无线MCU(如QN/JN/KW产品系列)。在新发布的i.MX RT上,集成了可用于显示和摄像的像素处理加速管道,以及i.MX 7系列的ARM Cortex-A7+M4等配置。在今后的产品路线图中,恩智浦会在多种异构集成上持续创新,助力行业的整体进步。

(内容提供:宋岩 恩智浦半导体微控制器业务线高级工程师)

下面,我们就一起来“品尝”一下恩智浦的几款异构集成处理器的“味道”。

LPC541xx基于高能效的ARM Cortex-M4内核,部分型号还选配了Cortex-M0+内核。这个M4与M0+的异构集成给开发者带来了很多方便和可能。比如,当系统中有高频率的中断要响应,或者不规则的数据搬运(像是在LCD上绘制一个矩形),M0+内核就大有用武之地了。在另一些重复性强且计算强度不大的图像处理中,M4与M0+则可以像两个人同时抢吃一盘豆一般,并行处理所有的像素,使得100MHz的MCU能达到150MHz单核的性能。另外对于一些需要组件隔离,比如软件由不同的开发团队维护的场合,两个内核可以运行各自开发的软件,从根本上降低了耦合度。

下一个出场的是跨界处理器i.MX RT1050。作为i.MX RT家族的成员,它完美融合了低功耗应用处理器和高性能微控制器的优势,能够以合理的价格提供超高性能ARM Cortex-M内核,实时功能和MCU的可用性。虽然这里高大上的M7独挑了主处理器的大梁,但它在图形图像处理上则集成了特色的像素处理管线,大大优化了显示与摄像应用的性能。