作者:吴均 一博科技高速先生团队队长

1、串行总线来了

绕线话题从开篇到结尾,花了好几个月哈,老是出差,没有时间静下来写东西。不过或许出差也只是借口,而是因为时序绕线这个话题实在是有点难写好吧。不管怎么说,挖下的坑是一定要埋上的,今天就是绕不完的等长的最后一篇,串行总线来了。

上一篇文章发出来之后,不少网友回复说,DDR3的同组数据并不需要做到5mil等长这么严格呀。看到这样的回复,高速先生们都是热泪盈眶:“同志,见到你真好……”。说实话,写这个系列文章还是有点私心的,希望以后不会再收到客户提出的+/-1mil,+/-0.5mil等长这样的要求,我们已经是很满足了。+/-5mil或者+/-10mil,这已经不是个事了,咬咬牙,加点班,这个等长我们就忍了。

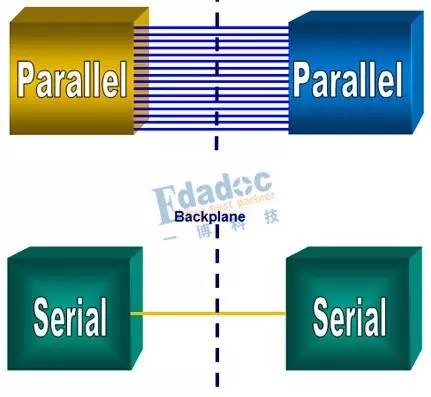

到了串行总线,貌似速率更高了,大家对等长的要求也更严格了。那么串行总线到底是什么鬼?

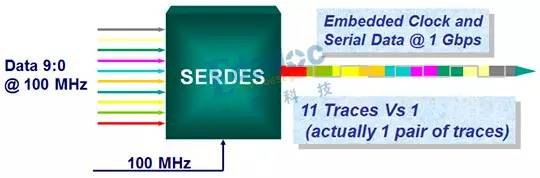

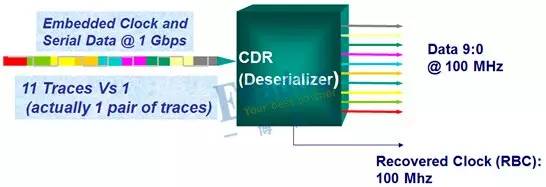

高速串行总线的技术核心是SerDes技术,也叫SerDes(Serializer-Deserializer)是串行器和解串器的简称。串行器(Serializer)也称为SerDes发送端(Tx),(Deserializer)也称为接收端Rx。下面一张图,轻松看懂SerDes的工作原理。

篇幅关系,也是高速先生的风格,我们不去解释SerDes的工作原理细节,从上图,我们只需要看懂:

-

时钟是内嵌在差分对里面的

-

到了接收端,时钟信号被重新恢复

2、高速串行总线(SerDes)的等长要求

从上文可以很容易得到结论:高速串行总线技术采用时钟和数据恢复技术,从而解决了限制数据传输速率的信号时钟偏移问题,减少布线冲突、降低开关噪声、更低的功耗和封装成本等。所以差分对与差分对之间基本没有等长要求;时钟是依赖串行解串的技术进行传输与恢复。

高速串行总线设计的难点从传统的时序问题,变成自身的Jitter,误码,损耗衰减等问题,关注的重点是差分对本身的信号质量,以及尽量避免受外界干扰影响。

差分对自身的问题,包括:

-

对内等长带来的相位问题以及差模共模模态转换

-

差分对间的串扰问题评估及优化

-

导体损耗,介质损耗等高频损耗问题

这些话题里面,差分相位及模态转换是绕线和走线拐角关注的问题点,会在这个时序系列里面进行探讨。其他问题则会在以后专门的高速串行总线系列来进行讨论。

注:说到高速串行总线基本没有差分对与差分对之间等长要求,需要注意的是差分线不完全等于高速串行总线;换句话说,高速串行总线基本都是差分形式,但是不是所有的差分线都是高速串行总线。

如果差分线不是高速串行模式,而是并行总线,等长设计按照之前导论的并行总线原则来执行(比如传说中还没有推出的差分版本DDR4)

既然说高速串行总线基本没有差分对与差分对之间等长要求,那么就还是有特例:

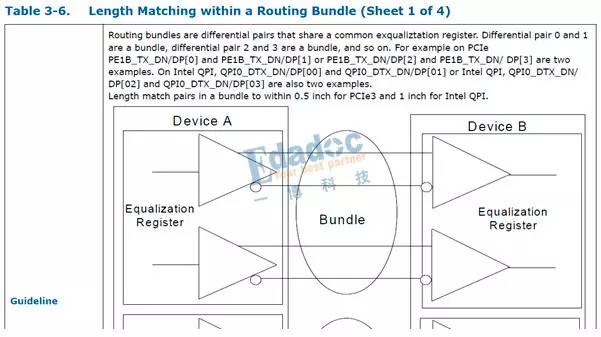

Intel的PDG里面,对同一Bundle内部的PCIE3信号和QPI信号提出了等长要求。不过这是一个很宽松的要求,正常的布局布线设计,基本是不用考虑绕线这个事情的。

回顾一下之前文章的要点,温故而知新嘛,现在不都是流行重要的事情多说几遍吗?

1、共同时钟总线的时序要求,不是等长,而是满足一个范围,更多的时候,需要注意不要走线太长。(这时候男女还没结婚,步调不一致,等长没有意义,大家看的是外部条件,需要满足一个基本要求)

2、源同步时钟总线的时序要求,主要是分组等长。但是等长只是满足了静态偏移,做到几个ps已经是足够好了(+/-10mil左右)。影响更大的是动态偏移,也就是SSN,ISI,Crosstalk等,不要过度强调等长(+/-1mil),而忽略了其他更重要的设计要求(这时候男女已经结婚了,步调一致最重要,只要夫妻齐心,Tco,飞行时间那都不是事。但是外部的风雨还是会影响感情,担心来自于电源噪声、串扰的影响)

3、高速串行总线,时钟内嵌,差分传输,更关注信号自身的品质,外部的干扰已经很难影响到时序了,需要关注差分线自身的设计质量(男女经过磨合,达到了灵魂伴侣的层次,只要两人同心,一切外部的事那都不是事了,所以关注的重点变成两人是否同心 - 差分)

相关阅读:

PCB设计十大误区-绕不完的等长(一)

PCB设计十大误区-绕不完的等长(二)

PCB设计十大误区-绕不完的等长(三)

PCB设计十大误区-绕不完的等长(四)

本文转载自:高速先生(作者:吴均)

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理(联系邮箱:cathy@eetrend.com)。