作者: Silicon Labs

在本单元秒懂时钟系列——噪声源时钟树第1部分案例,我们将超越原型或“标准”时钟树。我将对添加抖动衰减器的动机及其对时钟树抖动估计的影响进行讨论,所以让我们开始吧。

准时钟树

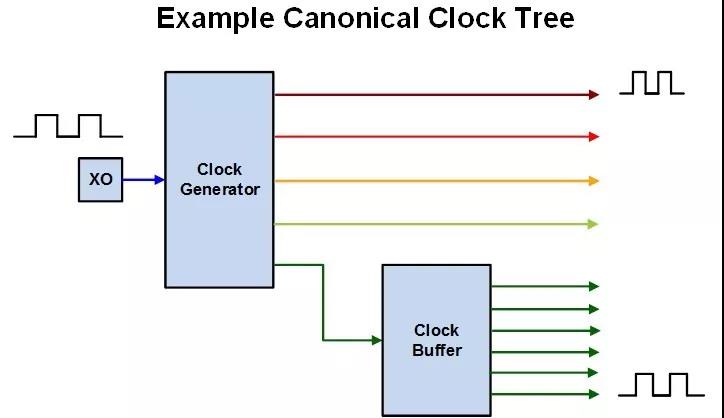

板级时钟树或时钟分配网络,例如数据中心应用,通常用晶体或低抖动XO(晶体振荡器)来描述,其连接到时钟发生器,后跟一个或多个缓冲器,如下所示。这就是我所说的标准时钟树:

在该示例中,时钟树的根或源是低抖动XO,其总体上确定时钟树的频率稳定性。紧接着,时钟发生器将输入频率从XO缩放到几个不同(通常更高)的输出频率。最后,时钟缓冲器采用这些输出频率之一并产生具有相同频率的多个输出时钟。图中的彩色箭头表示不同的时钟频率。

我们可以通过应用个别贡献的正方形的RSS或根和来估计标准时钟树的总时钟相位抖动或结束时钟相位抖动。(这与用于机械公差和其他误差或不确定性的级联统计分析的正交数学相同。)

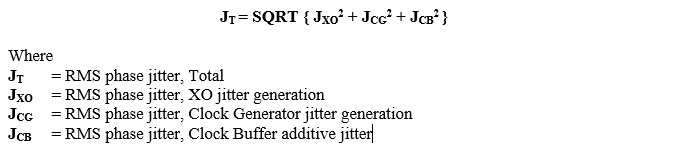

对于上面的示例,我们可以估计总RMS相位抖动为:

请注意,要使此计算有效,必须满足以下几个先决条件:

1、相位抖动贡献应该是不相关的。

2、每个相位抖动贡献必须在相同的抖动带宽上进行集成,例如, 12 kHz至20 MHz。

3、最后,时钟树中的每个器件都是相关时钟的宽带。

抖动转移vs抖动发生vs附加抖动

上面的最后一个声明意味着与输入时钟相位噪声相比,只要时钟发生器的带宽足够宽,那么我们就不需要考虑时钟发生器的抖动转移。你可能还记得,抖动转移或抖动衰减可测量输出时钟抖动与输入时钟抖动的关系。这通常写为抖动传递函数或JTF。PLL的JTF用作输入抖动的低通滤波器,是PLL带宽的函数。

抖动生成是指器件的固有抖动。在时钟发生器的情况下,它是在应用理想(无抖动)输入时钟时的输出抖动的度量。基于PLL的时钟器件即使具有完美的输入时钟,仍具有PFD(相位频率检测器)路径噪声和固有相位噪声源VCO。因此抖动生成项是需要的。

相比之下,仅由放大器和可能的分频器组成的时钟缓冲器将始终为任何输入时钟提供额外的噪声。因此使用术语加性抖动。

噪声来源案例

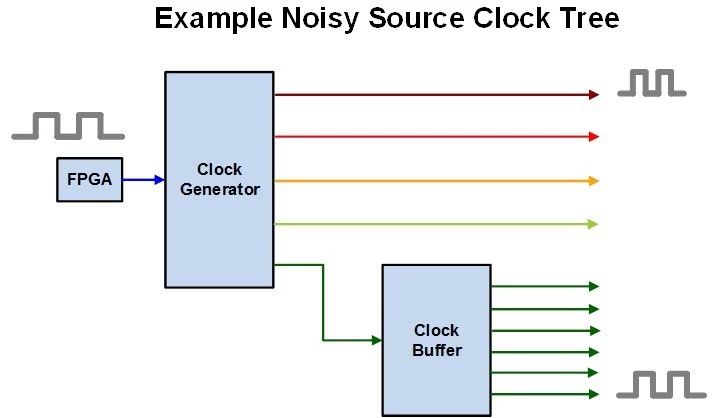

上述的示例规范时钟树假定如在典型应用中的低噪声时钟,然而,并非所有时钟树都具有低噪声时钟源。

是什么将源时钟归类为相对较低或较高的噪声呢?让我们暂时忽略后续时钟缓冲器,只是比较XO的抖动生成与时钟发生器的抖动生成。如果它们完全相同,则总抖动将增加SQRT(2)或实质上的41%。如果我们选择增加10%的通常工程惯例来表示重要性,那么我们可以退出——因为这时XO的相位抖动应该小于时钟发生器相位抖动的46%。换句话说,源抖动必须接近时钟发生器抖动的一半,以显着增加输出时钟抖动。

噪声(抖动)时钟可以是来自串行数据的恢复时钟或来自FPGA。电路板也许本身正在向XO引入电源噪声。紧接着这样的时钟树表现如下图所示。此处显示的波形比上图中的波形更粗,表明抖动更高。

即使对于噪声源时钟,我们仍然可以应用RSS估计。但是,对于典型的时钟分配应用,通常产生的抖动太高。那么什么是我们的来源?

抖动衰减器的应用

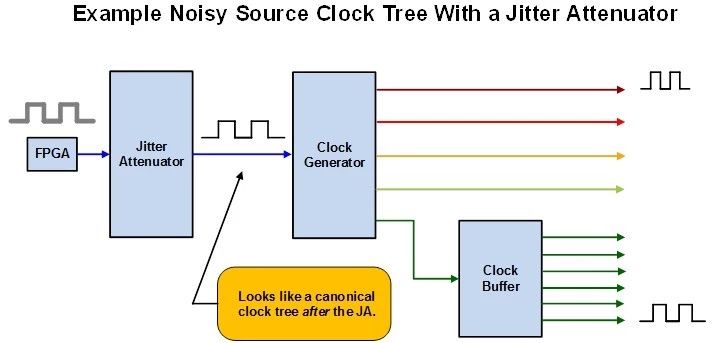

在这些应用中,我们需要添加一个抖动衰减器来清除源时钟噪声并改善时钟树抖动性能。下图说明了我们在噪声FPGA源时钟和时钟发生器之间插入抖动衰减器的基本思路。现在后抖动衰减器以及时钟树的其余部分看起来像标准情况。但是请注意,在实际应用中,单个器件通常执行抖动衰减器和时钟发生器缩放这些功能。

与时钟发生器一样,抖动衰减器是基于PLL的器件,其JTF充当输入抖动的低通滤波器。然而,与时钟发生器不同,抖动衰减器是相对窄的带宽器件,而不是输入时钟相位噪声。这违反了使用RSS估算方法的先决条件之一。那么,计算抖动衰减器输出时钟的预期相位抖动以及扩展总时钟抖动或结束时钟抖动的最佳方法是什么?

相位噪声处理系统——时钟树

在工程领域,我们通常会分析和测量频域中系统的性能。时钟分配网络,也称时钟树,它也不例外。时钟的主要属性是其频率,RMS相位抖动量是从相位噪声数据中集合而来。毫无疑问,分析时钟树更好和更严格的方法通常是在频域中。

事实上,从源头通过抖动衰减器,时钟发生器或乘法器以及缓冲器到时钟信号或目标的时钟信号被视为最佳的处理相位噪声系统(“一个人的噪声是另一个人的信号”为例)。

特别是抖动衰减器的应用只能通过在频域中工作才能很好地理解。JTF可以简单地通过PLL带宽和感兴趣的抖动带宽中的预期衰减来建模。在每个相位噪声偏移频率f,我们根据JTF形成的输入时钟相位噪声计算输出时钟相位噪声,并且与抖动生成相位噪声贡献正交相加。然后,我们可以检查所产生的集成相位抖动是否满足所需的抖动性能。

我将更详细地讨论如何执行此操作,并在下一篇文章“噪声源时钟树第2部分的案例”中提供测量和电子表格示例。

相关阅读:

秒懂时钟: 抖动衰减时钟设计与应用技巧 – Part 1

秒懂时钟-抖动衰减时钟设计与应用技巧 – Part 2

秒懂时钟-抖动衰减时钟设计与应用技巧 – Part 3 : Clocktoberfest

秒懂时钟-抖动衰减时钟设计与应用技巧Part 4: 拆分终端

秒懂时钟Part 5: PLL的VCO高通传递函数案例

秒懂时钟Part 6: 时钟相位噪声测量中的杂散

秒懂时钟Part 7: 探讨时钟相位噪声测量中的杂散(下篇)

秒懂时钟Part 8: 探讨RMS周期抖动的经验法则

秒懂时钟Part 9: 探讨不符合的测量范围造成失准的因素

秒懂时钟Part 10-半终端差分输出时钟的情况

本文转载自:SiliconLabs

声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有,如涉及侵权,请联系小编邮箱:cathy@eetrend.com 进行处理。