近期我们一直在做一些内部培训,一个常见的问题就是锁相环(PLL)如何以及为什么会根据输入时钟还是VCO(压控振荡器)的不同来处理相位噪声。大多数人都明白,输入时钟相位噪声是抖动衰减的,即PLL起着低通滤波器的作用来输入相位噪声。然而,为什么一个PLL应该像VCO相位噪声的高通滤波器那样工作并不明显。这是PLL的VCO高通传递函数的案例,也是本月的主题。

首先,我将回顾基本的反馈回路及其传递函数。接下来,我将概括在环路周围不同位置注入信号的过程。然后,我将根据输入时钟和VCO的角度生成并比较PLL的传输函数。最后,我将通过提供一些例子和讨论应用程序的考虑来总结。

反馈评论

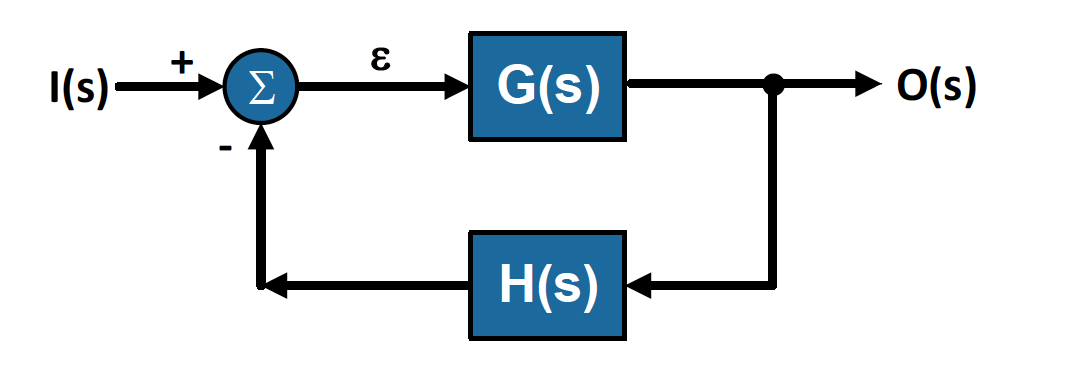

考虑下图中的基本反馈图,其中变量和块是拉普拉斯复变频率变量的函数。中间变量 S表示应该被考虑的错误. 正向增益是G(s)和反馈增益H(s)。 I(s)和O(s)分别是输入和输出信号。

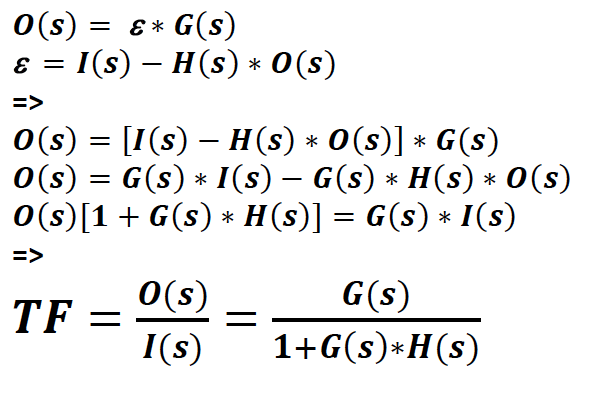

O(s)/I(s)的闭环传递函数TF推导如下。

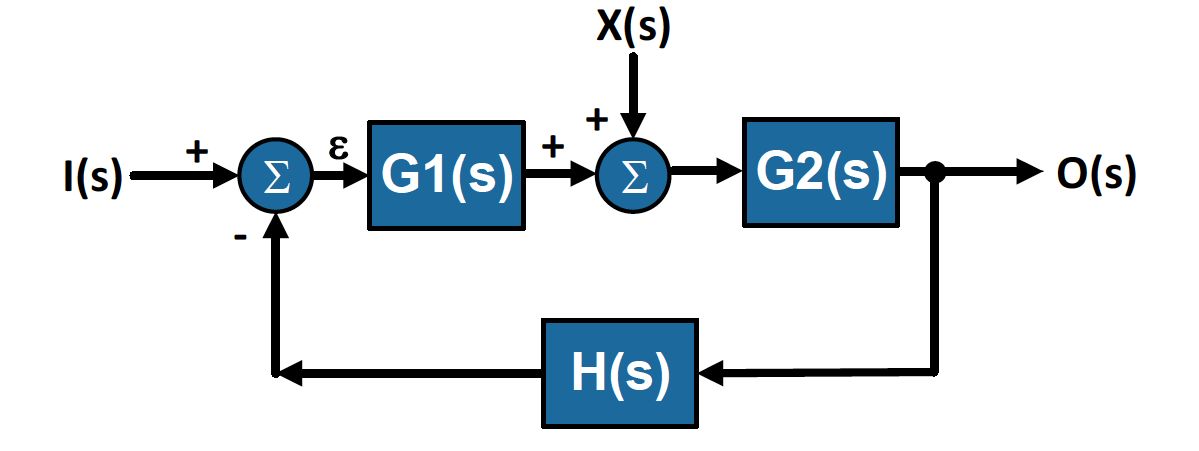

现在如果我们将前向路径增益G(s)分解成两个独立的块G1(s)和G2(s)并注入一个新的信号X(s),如下所示,会发生什么? X(s)与噪声一样是累加的。

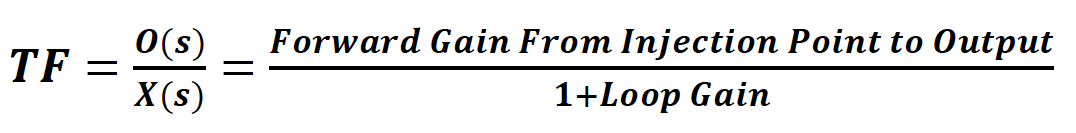

通过线性,O(s)/x(s)的传递函数TF如下推导,其中I(s)被设置为0。

事实证明,我们可以泛化如下反馈回路周围的任何X(s)注入点。术语“环路增益”是指在闭环周围的所有增益单元的乘。在这个特定的例子中,环路增益= G1(s)*G2(s)*H(s)。

我们现在可以将这些应用到基本的PLL。

输入时钟相位噪声传递函数

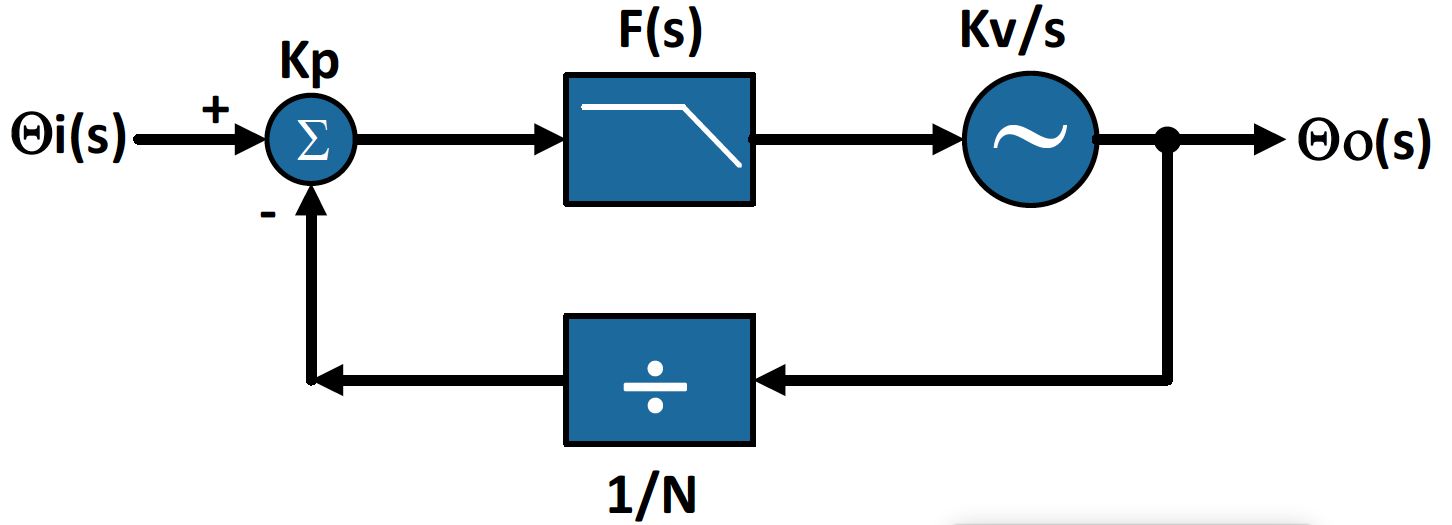

考虑下面的基本线性“小信号”PLL图。

顺时针循环,图中的组件如下。

· Kp表示相位检测器的增益,通常是PFD(相位频率检测器)。

· F(s)是作为复数频率“s”的函数的低通滤波器。

· Kv是VCO的增益,1 / S表示VCO的积分作用。也就是说,Kv *相的积分的拉普拉斯变换是Kv / s。

· 1 / N是反馈分频器的增益。

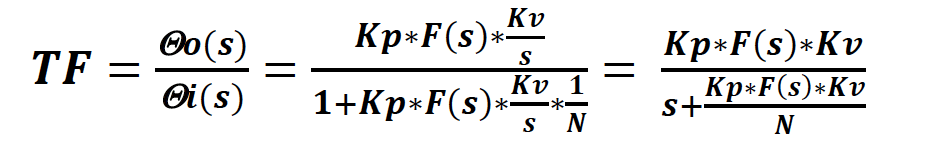

我们现在几乎可以通过检查正向增益为KpF(s)Kv/ s,环路增益为[KpF(s)Kv/ s] / N来生成Theta_o(s)/Theta_i

出于稳定的原因,F(s)始终是一个低通滤波器,因此其值或者是常数值,或者随着频率的增加而下降。无论哪种情况,PLL的整体闭环行为本身就是一个低通滤波器。

在许多教科书和文章中都介绍了这种PLL传递函数,但是Peter Delos在2016年1月出版的“高频电子学”中的文章“Phase Locked Loop Noise Transfer Functions” 中包含了有关该主题的更详细和最近的讨论。

VCO相位噪声传递函数

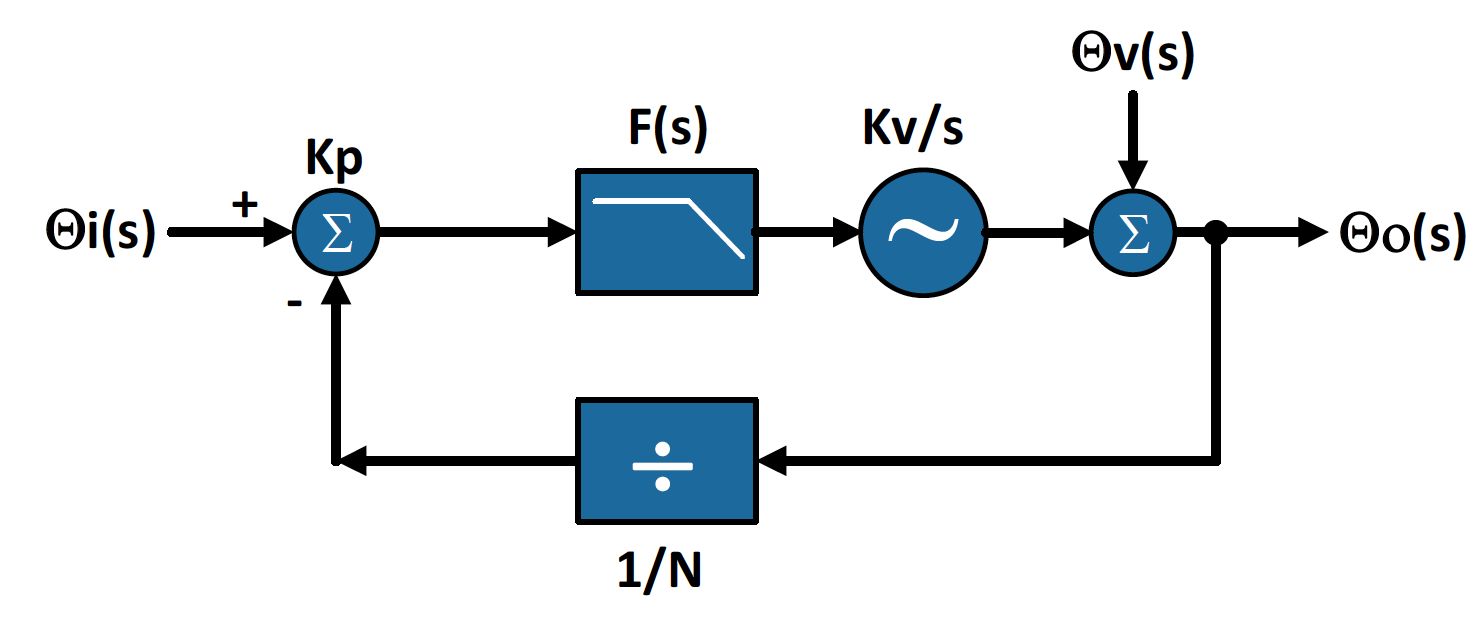

现在考虑下面修改的基本PLL图,以通过变量Theta_v(s)注入VCO相位噪声。

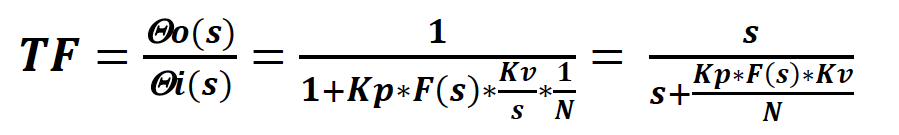

我们可以通过注意到来自VCO相位噪声注入点的前向增益简单地为单位并且环路增益如前所述[KpF(s)Kv/ s] / N来产生Theta_o(s)/Theta_v(s)的TF。

同样,F(s)是一个低通滤波器,所以它的值或者是不变的或者是降的。与输入时钟的传递函数不同,分子在原点处有一个零点。在这种情况下,PLL的整体闭环行为现在是一个高通滤波器。

直观例子

好吧,我知道你们中的一些人可能会说,我得到了数学,但是我并没有直观地理解为什么PLL作为VCO相位噪声的高通滤波器。让我提供一些直观的例子。

考虑Theta_i与Theta_v相位步骤的预期行为差异:

-

我们知道Theta_i的相位步骤不会立即在Theta_o输出。相反,取决于环路带宽,PLL将需要一些时间来响应,并适当地逐步调整输出相位以跟踪输入时钟相位的变化。这类似于施加到低通滤波器的电压阶跃。

-

相反,由于Theta_v输出的相位阶跃必须立即在Theta_o输出。没有什么可以阻止这一点。循环然后必须把事情正确地为了正确地追踪输入时钟。根据环路带宽的不同,输出时钟需要一段时间才能失去过多的相位。这种行为类似于应用于高通滤波器的电压阶跃。

用注意事项

PLL中两个主要的相位噪声源通常是输入时钟和VCO。正如我们所看到的,PLL分别对待每个噪声源的噪声,即分别作为低通滤波器和高通滤波器。

应用的结果如下:

1、如果输入时钟相对于VCO具有相对较低的相位噪声,则通常使用相对宽带宽(BW)PLL来衰减VCO的相位噪声。在这种情况下,宽带宽通常意味着大约为kHz至MHz的数量级。这是如何设计时钟发生器或时钟倍频器的。(注意,由于稳定性和抑制鉴相器杂散的需要,BW不能任意大。)

2、另一方面,如果输入时钟相对于VCO具有相对较高的相位噪声,则通常使用相对窄的带宽PLL来衰减输入时钟的相位噪声。在这种情况下,窄带宽是指kHz以下的量级,通常要小得多。这是如何设计抖动衰减器。

理解这种折衷以及调整带宽“旋钮”的能力是解决PLL和优化其应用的关键。

结论

本月我已经回顾了PLL的VCO相位噪声传递函数是如何产生的以及它独特的高通行为。我也提供了一些例子,并讨论了应用的考虑事项。

相关阅读:

秒懂时钟: 抖动衰减时钟设计与应用技巧 – Part 1

秒懂时钟-抖动衰减时钟设计与应用技巧 – Part 2

秒懂时钟-抖动衰减时钟设计与应用技巧 – Part 3 : Clocktoberfest

秒懂时钟-抖动衰减时钟设计与应用技巧Part 4: 拆分终端

本文转载自: SiliconLabs

转载地址:http://mp.weixin.qq.com/s/t5wYW4a1tGDHsVqVtNOJEg

声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有,如涉及侵权,请联系小编进行处理。